# Penn State III-V Tunnel FET Model Manual Version 1.0.1

Huichu Liu, Vijaykrishnan Narayanan, Suman Datta

Microsystem Design Lab (MDL) & Nanoelectronic Devices and Circuits Lab (NDCL) The Pennsylvania State University, University Park, PA 16802 Last Update: April 15, 2015

# Penn State III-V Tunnel FET Verilog-A Model Manual (Version 1.0.1)

# **Table of Contents**

| 1   | Intro | roduction2                                                |    |  |  |

|-----|-------|-----------------------------------------------------------|----|--|--|

| 2   | III-V | Tunnel FET (TFET) Device Simulation and Model Calibration | .2 |  |  |

|     | 2.1   | Tunnel FET Device Design and Simulation                   | .2 |  |  |

|     | 2.2   | InAs Homojunction TFET Model Calibration                  | .4 |  |  |

| 2.3 |       | GaSb-InAs Heterojunction TFET Model Calibration.          | .5 |  |  |

|     | 2.4   | Capacitance Characteristics                               | .6 |  |  |

|     | 2.5   | Experimental Data Reference                               | .7 |  |  |

| 3   | TFE   | T Verilog-A Models                                        | 10 |  |  |

|     | 3.1   | Look-up Table based Verilog-A Model                       | 10 |  |  |

|     | 3.2   | Model Description (Ver. 1.0.1)                            | 11 |  |  |

|     | 3.3   | Terminal and Voltage Definition for Intrinsic Device      | 14 |  |  |

|     | 3.4   | DC Characteristics                                        | 14 |  |  |

|     | 3.5   | Transient Characteristics                                 | 14 |  |  |

|     | 3.6   | Pseudo P-TFET                                             | 15 |  |  |

| 4   | Exa   | mple Circuits and Spectre Simulation Results              | 15 |  |  |

|     | 4.1   | Id-Vg simulation: DC Analysis Example                     | 15 |  |  |

|     | 4.2   | TFET based Inverter: Transient Analysis Example           | 17 |  |  |

|     | 4.3   | HTFET based Ring Oscillator: Transient Analysis Example   | 19 |  |  |

| 5   | Refe  | ferences                                                  |    |  |  |

#### **1** Introduction

We presented look-up table based Verilog-A models for III-V interband Tunnel Field Effect Transistors (TFETs) based on the calibrated TCAD Sentaurus [1] device simulations. The Verilog-A models can be further implemented to Spectre [2] circuit simulators. The calibrated TFET TCAD models serve as an approximation of full-band atomistic calculation of TFET band diagram and band-to-band tunneling current to generate the DC characteristics [3]. The gate-source and gate-drain capacitance characteristics obtained from the TCAD small-signal simulation has recently been validated with the measured transient characteristics of TFET [4, 5], which are employed for circuit-level transient analysis.

To improve the tunneling current, low bandgap materials (e.g. SiGe, Ge, InGaAs, InAs) have been widely explored for TFET prototype device design. The demonstrated double-gate III-V heterojunction TFET exhibits MOSFET-like on-current [6, 7, 8]. The improved gate-electrostatic control can further reduce the sub-threshold slope [9, 10]. Two types of III-V TFETs are considered for model development based on double-gate, ultra-thin body structure: InAs homojunction TFET and GaSb-InAs near-brokengap heterojunction TFET. Our Veriog-A models can capture TFET DC and transient operation for a wide range of operating voltages, which are suitable for various small-scale circuit designs and performance benchmarking (e.g. power consumption, energy-delay). Details of device calibration, look-up table generation and Verilog-A model implementation for circuit analysis are described in this manual.

# 2 III-V Tunnel FET (TFET) Device Simulation and Model Calibration

# 2.1 Tunnel FET Device Design and Simulation

TFETs have asymmetrical source/drain doping which operates as reverse-biased, gated p-i-n tunnel diodes. In TFETs, the on-off switching is enabled by the gate-voltage induced band-to-band tunneling (BTBT) at the source-channel tunnel junction. In conventional MOSFETs, only the carriers with energy exceeding the source-channel thermal barrier contribute to the on-state current. These carriers follow the Fermi-Dirac distribution with an energy slope of kT (where k is the Boltzmann constant, T is the absolute temperature), which induces a thermal limited sub-threshold slope of 60 mV/decade (~2.3kT/q at 300K, where q is the unite charge). In TFETs, the high energy carriers are filtered by the gate-controlled tunneling window. As a result, a sub-60 mV/decade SS, in principle, can be achieved in TFETs at the room temperature (300K) [11].

High on-state current (I<sub>on</sub>), high on-off ratio and steep SS are critical aspects in TFET design, which allow the further scaling of the supply voltage (V<sub>DD</sub>) for power consumption reduction without jeopardizing the performance. Tremendous progress has been made in TFET prototype demonstration with significant improvement of the tunneling limited I<sub>on</sub> and reduction of SS. The design of TFET involves the tunneling barrier reduction (e.g.

low bandgap materials, hetero-band-alignment), gate electrostatics improvement (e.g. multi-gate or gate-all-around, ultra-thin body, effective oxide thickness (EOT) reduction), and low interface states to suppress the trap-assisted tunneling (TAT) [6-10]. III-V semiconductors are attractive for TFET fabrication due to their direct band-gaps and wide range of compositionally tunable band-alignment for tunnel barrier reduction. Previous work in [6, 7, 8] demonstrated III-V heterojunction TFET (HTFET) with MOSFET-like on-current through the reduction of effective tunneling barrier width while preserving the band-gap of the channel material to achieve a simultaneous enhancement of the on-off ratio. Benchmarking on beyond CMOS logic devices in [12] shows significant energy efficiency advantages in HTFET, where over 10<sup>15</sup> Integer Ops/s/cm<sup>2</sup> with power consumption less that 1W/cm<sup>2</sup> can be achieved.

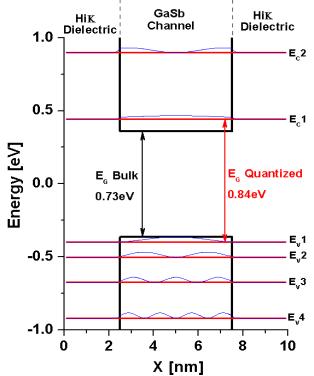

Figure 1. Example of the effective bandgap of GaSb due to quantization obtained from nextnano [14] simulation.

For TFET device simulation, the full-band atomistic simulation provides an accurate calculation of the band-to-band tunneling (BTBT) [13] for ideal device performance evaluation (e.g. defect free case). TCAD simulation serves as an approximation for the BTBT generation calculation based on the dynamic non-local tunneling model, which requires calibration with atomistic full-band simulation. Figure 1 shows an example to obtain material characteristics from nextnano simulation [14] as parameter input for TCAD Sentaurus to account for the quantization effect. This section will be focusing on the TCAD simulation for InAs homojunction TFET and GaSb-InAs heterojunction TFET, which are used to generate the look-up tables in Verilog-A models.

#### 2.2 InAs Homojunction TFET Model Calibration

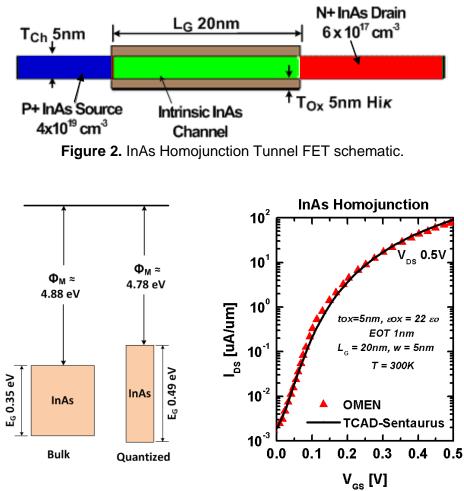

Double-gate InAs Homojunction Tunnel FET

Figure 3. InAs homojunction Tunnel FET DC characteristics calibration.

The double-gate InAs homojunction TFET schematic is shown in Figure 2 corresponding to the simulation structure in [22], which has a gate length ( $L_G$ ) of 20 nm, ultra-thin body (T<sub>Ch</sub>) of 5 nm, high-k dielectric thickness (HfO<sub>2</sub>) of 5 nm at EOT of 1 nm with the source/drain doping of  $4x10^{19}$  cm<sup>-3</sup> (p+) and  $6x10^{17}$  cm<sup>-3</sup> (n+), respectively. The quantization induced bandgap broaden was obtained through nextnano simulation as described above in Figure 3. The calibrated DC characteristics show good agreement with the atomistic full-band simulation results [3].

## 2.3 GaSb-InAs Heterojunction TFET Model Calibration.

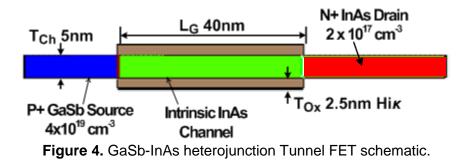

Double-gate GaSb-InAs Heterojunction Tunnel FET

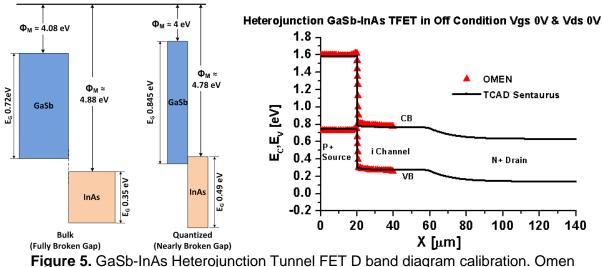

Figure 4 shows the GaSb-InAs heterojunction FET schematic, which is calibrated with simulated structure in [3] with a gate length (L<sub>G</sub>) of 40 nm, ultra-thin body (T<sub>Ch</sub>) of 5 nm, high-k dielectric thickness (HfO<sub>2</sub>) of 5 nm at EOT of 1 nm with the source/drain doping of  $4x10^{19}$  cm<sup>-3</sup> (p+) and  $2x10^{17}$  cm<sup>-3</sup> (n+) respectively. The quantized bandgap are shown in Figure 5 which agrees well with the OMEN simulation in [13]. The effective barrier height (E<sub>beff</sub>) is 0.065 eV.

simulation results are obtained from [13].

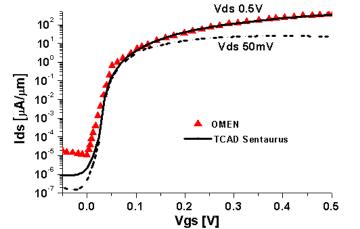

Figure 5 shows the calibration of DC characteristics obtained from TCAD simulation with OMEN simulation results. The current at 0.5 V  $V_{ds}$  shows good match at sub-threshold region and super-threshold region. Note that leakage current from TCAD simulation was 1 order lower. The Verilog-A model of GaSb-InAs HTFET uses 20 nm gate-length derived from this calibrated model.

Heterojunction GaSb-InAs TFET IdVg : TCAD & OMEN

Figure 6. GaSb-InAs heterojunction TFET DC characteristics calibration.

#### 2.4 Capacitance Characteristics

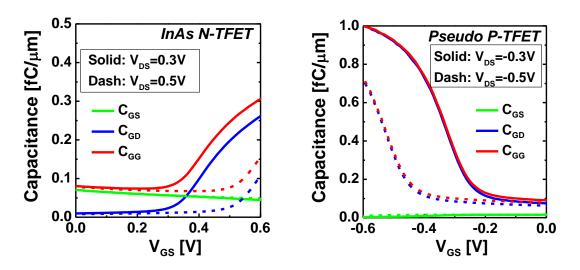

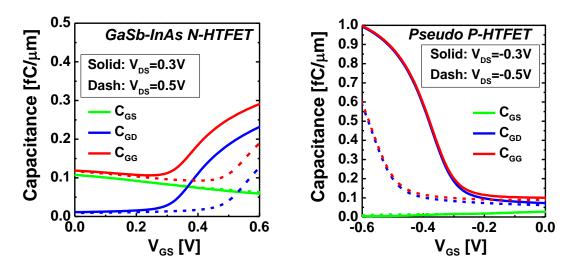

Capacitance characteristics are critical for accurate device modeling. Due to the semiclassical simulation nature of TCAD, TFET gate-source C<sub>gs</sub> and gate-drain capacitance C<sub>gd</sub> characteristics obtained from the small signal simulation requires validation from transient measurements. [15] first reported the unique capacitance characteristics of TFET, which is known as enhanced on-state Miller capacitance effect, showing a dominant  $C_{gd}$  among the total capacitance  $C_{gg}$  at the device on-state ( $V_{gs}=V_{DD}$ ). Such characteristics rises from the un-equal charge sharing between source and drain due to the tunnel-barrier, which results in a large "voltage spike" during transient analysis in TFET based inverter as compared to MOSFET case. Furthermore, Zhang et al [16] reported a Si TFET compact model based on the surface potential calculation, which shows the same observation (enhanced Miller capacitance effect) during transient analysis. Knoll et, al in [4] first reported the transient measurements of a Si nanowire TFET inverter, which further validates the effect of enhanced C<sub>gd</sub> contribution to overall C<sub>gg</sub>. Recently, Bijesh et al in [7] reported the first measured RF characteristics of fabricated near-broken gap III-V HTFET, showing a good match of the capacitance characteristics from TCAD with the extracted capacitance values, transconductance (gm) and cut-off frequency (f<sub>T</sub>) from S parameter measurements. More works [17, 18] have recently explored this unique capacitance characteristic of TFET. Based on the experiment validation, we obtain the capacitance characteristics of C<sub>gs</sub> and C<sub>gd</sub> using calibrated TCAD model to construct the TFET Verilog-A model. The capacitance characteristics of InAs TFET and GaSb-InAs HTFET are shown in Figure 7 and Figure 8.

Figure 7. C<sub>gs</sub>, C<sub>gd</sub> vs V<sub>gs</sub> characteristics for InAs homojunction TFET

Figure 8. Cgs, Cgd vs Vgs characteristics for GaSb-InAs heterojunction TFET

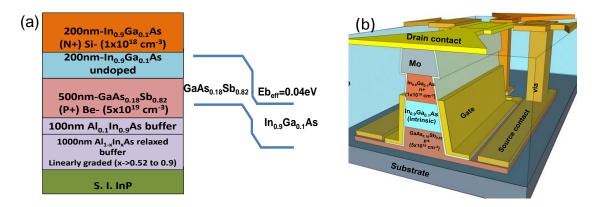

#### 2.5 Experimental Data Reference

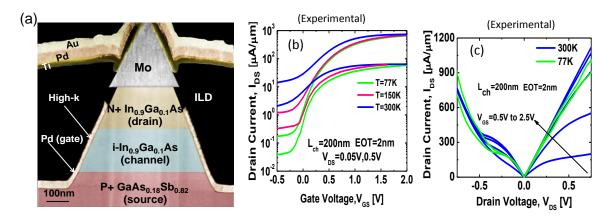

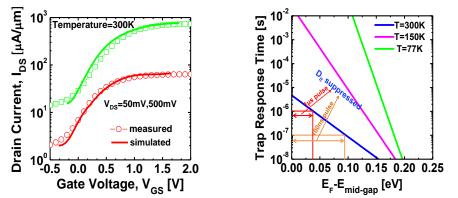

Due to the lack of experimental data, the simulation model validation of the 20 nm GaSb-InAs heterojunction Tunnel FET remains challenging. Here, we present the validation of our simulation models at a channel length of 200 nm with the fabricated near-broken gap heterojunction TFET from [7]. Figure 9 shows the In<sub>0.9</sub>Ga<sub>0.1</sub>As/GaAs<sub>0.18</sub>Sb<sub>0.82</sub> material system and the vertical Tunnel FET schematic [7]. The device TEM cross-section is shown in Figure 10(a). Benefited from the near broken gap induced high band-to-band tunneling current density, a high drive current of 740  $\mu$ A/ $\mu$ m is achieved at V<sub>DS</sub> = 0.5 V (Figure 10(b-c)). The numerical simulation model has shown a good agreement with the measured I<sub>DS</sub>-V<sub>GS</sub> characteristics at T = 300 K, V<sub>DS</sub> = 0.5 V using interface states density (D<sub>it</sub>) of 5x10<sup>12</sup>cm<sup>-2</sup>eV<sup>-1</sup> as shown in Figure 11(a-b).

Figure 9. The near-broken gap In<sub>0.9</sub>Ga<sub>0.1</sub>As/GaAs<sub>0.18</sub>Sb<sub>0.82</sub> heterojunction n-type Tunnel FET (a) material system and device schematic [7].

**Figure 10**. (a) Cross-section TEM image of the fabricated HTFET showing angled sidewall and gatedrain overlap. (b) Temperature dependent transfer characteristics of HTFET showing improved ION/IOFF at low temperature (c) Output characteristics of HTFET at T=300K and T=77K [7].

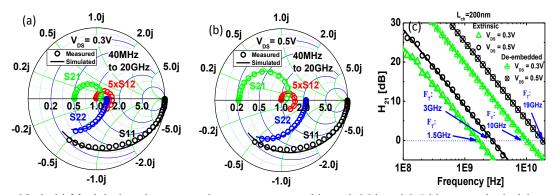

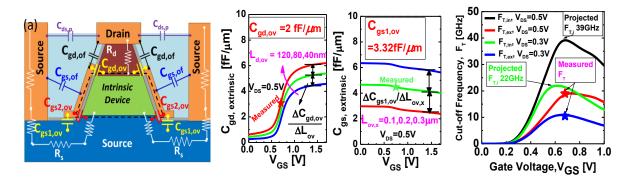

To validate the capacitance characteristics of the TCAD models, the RF measurement has been carried out with a coplanar ground-signal-ground (GSG) waveguide structure. Figure 12(a-c) shows the measured and modeled scattering parameters (S-parameters) to extract the cut-off frequency ( $F_T$ ) and capacitance values. The 200 nm HTFET exhibits a measured  $F_T$  of 10 GHz and 19 GHz at V<sub>DS</sub>=0.3V and 0.5V respectively. TCAD simulation of the HTFET device structure matched to the TEM image has been used taking into account parasitic capacitances and resistances. The capacitance characteristics and  $F_T$  of the TCAD models are obtained from the small signal simulation. The simulated  $C_{gs,extrinsic}$ ,  $C_{gd,extrinsic}$  values, as well as the  $F_T$  are in agreement with the measured values from RF measurements, as shown in Figure 13 [7]. The measured I<sub>DS</sub>-V<sub>GS</sub> characteristics and simulation results are available in the experiment data folder.

**Figure 11.** (a) TCAD simulation and measured characteristics at T=300K. (b) Simulated electron trap response time in In<sub>0.9</sub>Ga<sub>0.1</sub>As is used to estimate gate voltage pulse width required to suppress D<sub>it</sub>.

**Figure 12.** (a-b) Modeled and measured s-parameters at  $V_{DS} = 0.3$  V and 0.5 V respectively (c) Measured and modeled H<sub>21</sub> parameter at  $V_{DS} = 0.5$  V and 0.3 V. After de-embedding, F<sub>T</sub> of 10GHz and 19 GHz are measured at  $V_{DS}=0.3$  V and 0.5V respectively [7].

**Figure 13.** (a) 2D schematic of the simulated HTFET with dimensions calculated from the TEM with parasitic capacitances and resistance illustration. Extraction of (b) gate-drain overlap capacitance  $C_{gd,ov}$  (c) lateral gate-source overlap capacitance  $C_{gs1,ov}$  (d) Measured  $F_T$  is in agreement with the simulations. After de-embedding the overlap capacitances, HTFET with  $L_{ch}$ =200nm is expected to achieve  $F_T$  of 22GHz and 39GHz at V<sub>DS</sub>=0.3V and 0.5V respectively.

#### 3 TFET Verilog-A Models

#### 3.1 Look-up Table based Verilog-A Model

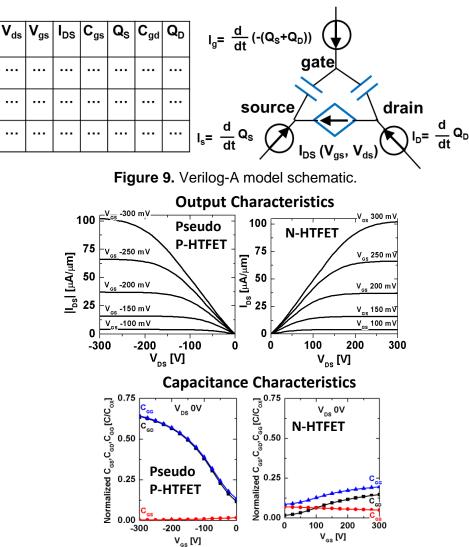

Lookup table-based Verilog-A model has been employed for TFET-based circuit designs in many literatures [3, 19, 20, 21]. Here we show the schematic of the Verilog-A transistor model in Figure 9 from [3]. It is a lookup table-based model composed of two-dimentional tables: the transfer characteristics  $I_{ds}(V_{ds}, V_{gs})$ , the gate-source capacitance  $C_{gs}(V_{gs}, V_{ds})$ and the gate-drain capacitance  $C_{gd}(V_{gs}, V_{ds})$  across a range of fine-step drain-source voltage bias  $V_{ds}$  and gate-source voltage bias  $V_{gs}$ . The TCAD models used for lookup table generation are the same as those shown in the previous Section 2, except that the gate lengths are all set to  $L_G$ =20 nm. The parasitic series resistance and parasitic external capacitance are not included in the TCAD model, which can be added at the circuit level as shown in the schematic above.

Figure 10. Device characteristics comparison.

Due to the ongoing efforts of p-type Tunnel FET development, we assume identical drivecurrents for the n-channel and p-channel transistors in TFET Verilog-A models for the optimal circuit performance. We should notice that the Density-of-States (DoS) of electrons and holes can be quite different in III-V materials, such that the gatecapacitance characteristics need to be obtained from TCAD simulation for n-type and ptype TFET, respectively, to accurate modeling the circuit performance. We develop a symmetrical device structure as n-type TFET to obtain the capacitance characteristics for pseudo p-type TFET. The p-type and n-type device characteristics of GaSb-InAs TFET are shown in Figure 10.

## 3.2 Model Description (Ver. 1.0.1)

The Verilog-A model is coded in ".va" file, which contains the following files:

| Wrapper File   |                | homotfet.va (for InAs Homojunction TFET);         |

|----------------|----------------|---------------------------------------------------|

|                |                | heterotfet.va (for GaSb-InAs Heterojunction TFET) |

| Master Model F | ile            | tfet_master.va                                    |

| Look-up        | InAs           | IdVg-InAs-NTFET-Lg-20nm.tbl,                      |

| Tables         | Homojuntion    | CGS-InAs-NTFET-Lg-20nm.tbl,                       |

|                | TFET           | CGS-InAs-PTFET-Lg-20nm.tbl,                       |

|                |                | CGD-InAs-NTFET-Lg-20nm.tbl,                       |

|                |                | CGD-InAs-PTFET-Lg-20nm.tbl;                       |

|                | GaSb-InAs      | IdVg-GaSb-InAs-HNTFET-Lg-20nm.tbl,                |

|                | Heterojunction | CGS-GaSb-InAs-HNTFET-Lg-20nm.tbl,                 |

|                | TFET           | CGS-GaSb-InAs-HPTFET-Lg-20nm.tbl,                 |

|                |                | CGD-GaSb-InAs-HNTFET-Lg-20nm.tbl,                 |

|                |                | CGD-GaSb-InAs-HPTFET-Lg-20nm.tbl;                 |

The key features of this model bundle are:

- (1) "tfet\_master.va" combined all the model features for n-type and p-type homojunction and heterojunction TFETs. 'ifdef has been used to enable HOMOJUNCTION and HETEROJUNCTION features.

- (2) "homotfet.va" and "heterotfet.va" recall "tfet\_master.va" to enable different types of TFETs (e.g. "homotfet.va" enables "\_HOMOJUNCTION\_" for InAs Homojunction TFET in "tfet\_master.va", while "heterotfet.va" enables "\_HETEROJUNCTION\_" for GaSb-InAs Heterojunction TFET in "tfet\_master.va".

- (3) In "tfet\_master.va", a parameter, "type", has used to define n-type and p-type transistors, which needs to be specify in the circuit netlist.

The master model file "tfet\_master.va" is as follows:

\*\*\*\*\*

`include "constants.vams"

`include "disciplines.vams" // Header files, using Verilog-A language to describe a module function

module TFET(d,g,s);

inout d,g,s;

electrical g,d,s; // Device module name and terminal definition

real Ids, Cgs, Cgd,Qg, Qs, Qd; // Variables used in modeling. parameter real W=1 from (0:inf); //Device width "W", in micrometer unit. parameter string type = "n" from '{"n", "p"}; // Parameter "type" to specify n-type or p-type TFET.

integer direction; // Variable to specify the current direction in n-type or p-type TFET.

//Verilog-A model main body analog begin

`ifdef HETEROJUNCTION // GaSb-InAs Heterojunction TFET

//n-type TFET, reading current Ids, capacitance Cgs and Cgd values from look-up tables (tables are generated from Sentaurus TCAD simulation), current direction is 1. Variable values assigned from the lookup tables in ".tbl" are according to terminal voltage condition. In each table, the 1st column is Vds, 2nd column is Vgs, 3rd column is the current or capacitance value.

if (type == "n") begin

Ids=\$table\_model(V(d,s), (V(g,s)), "IdVg-GaSb-InAs-HNTFET-Lg-20nm.tbl","1LL,1LL"); Cgd=\$table\_model(V(d,s), (V(g,s)), "CGD-GaSb-InAs-HNTFET-Lg-20nm.tbl","1LL,1LL"); Cgs=\$table\_model(V(d,s), (V(g,s)), "CGS-GaSb-InAs-HNTFET-Lg-20nm.tbl","1LL,1LL"); direction =1;

end

//p-type TFET, reading current lds, capacitance Cgs and Cgd values from look-up tables

(tables are generated from Sentaurus TCAD simulation), current direction is -1.

else if (type == "p") begin

// We assume that the PTFET and NTFET drive currents are similar

Ids=\$table\_model(-V(d,s), (-V(g,s)), "IdVg-GaSb-InAs-HNTFET-Lg-20nm.tbl","1LL,1LL");

// We do not assume that the PTFET and NTFET gate capacitances are similar because the hole and electon DoS in InAs are significantly different

Cgd=\$table\_model(V(d,s), (V(g,s)), "CGD-GaSb-InAs-HPTFET-Lg-20nm.tbl","1LL,1LL"); Cgs=\$table\_model(V(d,s), (V(g,s)), "CGS-GaSb-InAs-HPTFET-Lg-20nm.tbl","1LL,1LL"); direction = -1;

end

```

'else 'ifdef HOMOJUNCTION // InAs Homojunction TFET

```

//Similarly, reading variable values from look-up tables, specify the current direction according to the "type".

```

if (type == "n") begin

```

```

Ids=$table_model(V(d,s), (V(g,s)), "IdVg-InAs-NTFET-Lg-20nm.tbl","1LL,1LL");

Cgd=$table_model(V(d,s), (V(g,s)), "CGD-InAs-NTFET-Lg-20nm.tbl","1LL,1LL");

Cgs=$table_model(V(d,s), (V(g,s)), "CGS-InAs-NTFET-Lg-20nm.tbl","1LL,1LL");

direction =1;

```

end

```

else if (type == "p") begin

Ids=$table_model(-V(d,s), (-V(g,s)), "IdVg-InAs-NTFET-Lg-20nm.tbl","1LL,1LL");

Cgd=$table_model(V(d,s), (V(g,s)), "CGD-InAs-PTFET-Lg-20nm.tbl","1LL,1LL");

Cgs=$table_model(V(d,s), (V(g,s)), "CGS-InAs-PTFET-Lg-20nm.tbl","1LL,1LL");

direction = -1;

end

`endif

```

//Calculate the charge Qgd, Qgs and Qg according to the capacitances, device width and the terminal voltages. Calculate the terminal current with respect to the charge.

```

Qd = (W*-1*Cgd)*(V(g,d));

Qs = (W*-1*Cgs)*(V(g,s));

Qg=-1*(Qd+Qs);

I(d,s) <+ direction*Ids*W;

I(g) <+ ddt(Qg);

I(s) <+ ddt(Qs);

I(d) <+ ddt(Qd);

```

end endmodule

#### 3.3 Terminal and Voltage Definition for Intrinsic Device

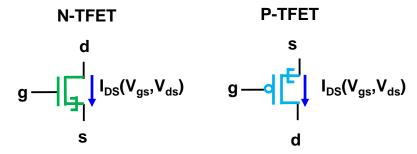

Figure 11. Terminal definition N-type TFET and p-type TFET and direction.

As shown in Figure 11, the intrinsic Tunnel FET (as shown in the dashed box in Figure 9) has 3 terminals: source (**s**), gate (**g**) and drain (**d**). No body terminal in this model due to the double-gate, ultra-thin-body device structure. The terminal voltage V(g,s) and V(d,s) identify the device operation and determine  $I_{ds}$ ,  $C_{gs}$  and  $C_{gd}$  at such  $V_{gs}$  and  $V_{ds}$  bias through the look-up tables:

```

module TFET(d,g,s);

inout d,g,s;

electrical g,d,s;

real Ids, Cgs, Cgd, Qs, Qd, Qg;

Ids=$table_model(V(d,s), (V(g,s)), "IdVg-NTFET_Lg2onm.tbl","1LL,1LL");

Cgd=$table_model(V(d,s), (V(g,s)), "CGD-NTFET_Lg2onm.tbl","1LL,1LL");

Cgs=$table_model(V(d,s), (V(g,s)), "CGS-NTFET_Lg2onm.tbl","1LL,1LL");

```

#### 3.4 DC Characteristics

The device DC current is directly obtained from the table value and device width (W) definition, and current direction (direction):

#### 3.5 Transient Characteristics

The device transient characteristics are obtained through charge models. Terminal charge of  $Q_{gd}$  (drain charge) and  $Q_{gs}$  (source charge) are calculated using  $C_{gd}$  and  $C_{gs}$  obtained from lookup tables and terminal voltages  $V_{gd}$  and  $V_{gs}$ , respectively. Since the

DC component of  $I_{gd}$  and  $I_{gs}$  are negligible, the transient current  $I_{gd}$  and  $I_{gs}$  are calculated according to the time evolution of the terminal charges:

```

Qd = (-1*W*Cgd)*(V(g,d));

Qs = (-1*W*Cgs)*(V(g,s));

Qg=-1*(Qd+Qs);

I(d,s) <+ direction*Ids*W ;

I(d) <+ ddt(Qd);

I(s) <+ ddt(Qs);

I(g)<+ddt(Qg);

```

## 3.6 Pseudo P-TFET

The pseudo P-TFET model uses the lds table of NTFET with P-TFET Capacitance characteristics:

if (type == "p") begin

Ids=\$table\_model(-V(d,s), (-V(g,s)), "IdVg-NTFET-Lg-20nm.tbl","1LL,1LL");

Cgd=\$table\_model(V(d,s), (V(g,s)), "CGD- PTFET-Lg-20nm.tbl","1LL,1LL");

Cgs=\$table\_model(V(d,s), (V(g,s)), "CGS- PTFET-Lg-20nm.tbl","1LL,1LL");

direction = -1;

end

#### 4 Example Circuits and Spectre Simulation Results

The TFET Verilog-A device model can be implemented in Spectre simulation. In order to execute the circuit simulations you need to have Virtuoso Spectre Circuit Simulator [2] installed. We present the following examples of using TFET Verilog-A model to obtain device Id-Vg characteristics, TFET based FO1 Inverter and Ring Oscillator simulation. The simulation projects are available with the model download as ".scs" files.

#### 4.1 Id-Vg simulation: DC Analysis Example

The Id-Vg simulation for NTFET is in ntfet\_idvg.scs. Run by:

>spectre ntfet\_idvg.scs

```

Note that, for InAs Homojunction TFET, use ahdl_include "homotfet.va"; for GaSb-Heterojunction TFET, use ahdl_include "heterotfet.va".

```

// Simulation language is Spectre.

simulator lang=spectre

global o

//Terminal voltages of VG and VD are defined as parameters. Device width is defined Width=1 um. Series resistance  $R_{Series}$  of 55 Ohm-um is used as parameter

parameters VG=0.0

parameters VD=0.3

parameters Width=1

parameters RSeries=55

//3 dc voltage sources V1, V2 and V3 are defined and connected to source, gate, and drain node.

- V1 (source 0) vsource type=dc dc=0

- V2 (gate o) vsource type=dc dc=VG

- V3 (drain o) vsource type=dc dc=VD

// R1 and R2 are the parasitic resistances I1 is the instance of an intrinsic NTFET with a width W=Width, where nodes d1, gate and s1 are connected to the device d, g, s terminals respectively. Parasitic resistance R1 and R2 are connected to NTFET's s and d, respectively. R1 (source s1) resistor r=RSeries/Width

//Specify type=n for NTFET

I1 (d1 gate s1) TFET type=n W=Width

R2 (drain d1) resistor r=RSeries/Width

dc dc param=VG start=0 stop=0.3 lin=100 oppoint=rawfile maxiters=150 \ maxsteps=10000 annotate=status

// Divide by two in order to report the current per micrometer. Since the simulator gives the double gate current

//print gate\*1000, -I(V3)\*1e6/2, name=dc addto="idvg\_heterotfet.out"

print gate\*1000, -I(V3)\*1e6/2, name=dc addto="idvg\_homotfet.out" //Print to file

//ahdl\_include "heterotfet.va" //Using ahdl to compile Verilog-A model ahdl\_include "homotfet.va" //Using ahdl to compile Verilog-A model

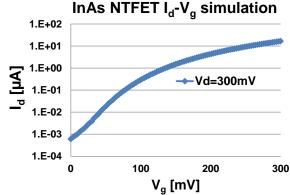

The simulation results of InAs Homojunction TFET are plotted in Figure 12.

**Figure 12.** Id-Vg of InAs N-TFET with source/drain series resistance of 55 ohm at  $V_{DS}=0.3V$ .

## 4.2 TFET based Inverter: Transient Analysis Example

The 5-stage FO1 inverter chain simulation using InAs TFET is in inverter\_InAs\_tfet\_FO1.scs. Run by:

>spectre inverter\_ tfet\_FO1.scs

Note that, for InAs Homojunction TFET, use ahdl\_include "homotfet.va"; for GaSb-Heterojunction TFET, use ahdl\_include "heterotfet.va".

\*\*\*\*\*

// Series resistance of 55 ohm-um and output parasitic capacitance 0.1 fF/um are included. Minimum device width  $W_{Min}$ =20 nm is used for simulation at  $V_{DD}$ =0.3V.

parameters VSUPPLY=0.3 INPUT=0

parameters RSeries=55

parameters CParasitic=100e-18

parameters WMin=0.02

V1 (supply1 o) vsource type=dc dc=VSUPPLY

V2 (gnd o) vsource type=dc dc=0

V3 (in1 o) vsource type=pwl wave=[0 0 1n 0 1.05n VSUPPLY 3n VSUPPLY 3.5n 0 5n 0]

//5-stage FO1 inverter chain

- X1 (out1 in1 supply1 gnd) inv

- X2 (out2 out1 supply1 gnd) inv

- X3 (out3 out2 supply1 gnd) inv

- X4 (out4 out3 supply1 gnd) inv

- X5 (out5 out4 supply1 gnd) inv

// Sub-circuit definition for TFET inverter which has 4 terminals: out, in, supply, gnd. Series resistance is added to PTFET and NTFET. Parasitic capacitance is added to the inverter output.

subckt inv out in supply gnd

#### // R1 R2 R3 and R4 are the parasitic resistances

R1 (01 out) resistor r=RSeries/WMin

I1 (01 in s1) TFET type=p W=1\*WMin

R2 (s1 supply) resistor r=RSeries/WMin

R3 (o2 out) resistor r=RSeries/WMin

I2 (02 in gnd2) TFET type=n W=1\*WMin

R4 (gnd2 gnd) resistor r=RSeries/WMin

#### // C1 is the parasitic output capacitance

```

C1 (out 0) capacitor c=CParasitic*WMin

ends

// Initial condition is given to inverter chain internal nodes.

ic out1=VSUPPLY out2=0 out3=VSUPPLY

```

tran tran stop=5n write="spectre.ic" writefinal="spectre.fc" annotate=status\ maxiters=5 autostop=yes print in1\*1000,out1\*1000,out2\*1000,out3\*1000,out4\*1000, name=tran\ addto="inv tran.out"

```

//ahdl_include "heterotfet.va" //switch to heterotfet

ahdl_include "homotfet.va" //switch to homotfet

```

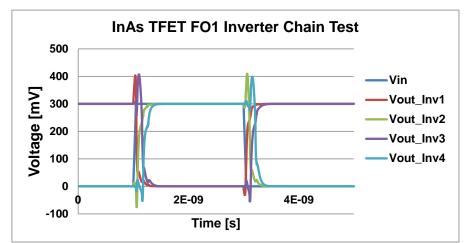

The simulation results are plotted in Figure 13.

Figure 13. Input and Output Waveforms of InAs TFET inverter with minimum sizing at  $V_{DS}$ =0.3V.

The measurement simulation to obtain fall-delay, fall-energy, rise-delay and rise-energy for signal-stage inverter can be obtained by running:

>spectremdl -b inverter\_ tfet\_FO1.mdl -d inverter\_ tfet\_FO1.scs -measure inverter\_ tfet\_FO1.measure

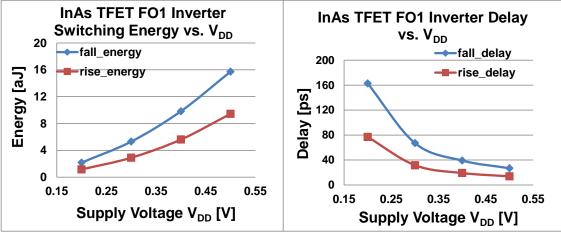

The output results (energy vs V<sub>DD</sub>, delay vs V<sub>DD</sub>) of InAs Homojunction TFET are shown in Figure 14.

Figure 14. InAs TFET FO1 Inverter Switching Energy and delay vs. supply voltage V<sub>DD</sub>.

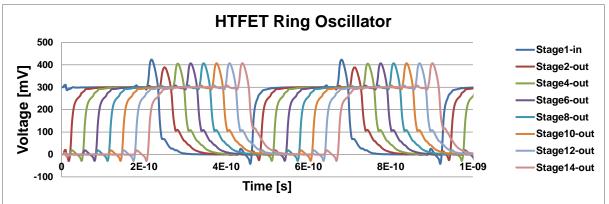

# 4.3 HTFET based Ring Oscillator: Transient Analysis Example

Similarly, the 15-stage FO1 inverter chain simulation using GaSb-InAs HTFET is in ring\_oscillator.scs. Run by:

>spectre ring\_oscillator.scs

The simulation results are plotted in Figure 15.

Figure 15. Input and output waveforms of GaSb-InAs HTFET NAND based ring oscillator at  $V_{\text{DS}} {=} 0.3 \text{V}.$

The measurement simulation to obtain fall-delay, fall-energy, rise-delay and rise-energy for signal-stage inverter can be obtained by running:

>spectremdl –b ring\_oscillator.mdl –d ring\_oscillator.scs –measure ring\_oscillator.measure

GaSb-InAs HTFET 15-stage Ring Oscillator

The simulation results are plotted in Figure 16:

**Figure 16.** Energy vs delay of the GaSb-InAs HTFET NAND based ring oscillator at different supply voltage V<sub>DD</sub>.

#### **5** References

- [1] Synopsis, TCAD Sentaurus Device Manual, 2010.

- [2] Cadence(R) Virtuoso Spectre Circuit Simulator, 2009.

- [3] V. Saripalli et al, "Variation-tolerant ultra-low-power heterojunction tunnel FET SRAM design," IEEE/ACM International Symposium on Nanoscale Architectures, vol. 1, pp. 45–52, Jun. 2011.

- [4] Knoll, L., et al, "Inverters with strained Si nanowire complementary tunnel field-effect transistors," in IEEE Elec. Dev. Lett., vol.34, no.6, p.813–815, June 2013.

- [5] Mookerjea, S. et. al, "On enhanced miller capacitance in interband tunnel transistors," in IEEE Elec. Dev. Lett., vol. 30, no.10, p. 1102–1104, Oct. 2009.

- [6] D. K. Mohata *et al*, "Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction Tunnel FETs with high drive current and high on-off ratio," *IEEE Symp.* on VLSI Technology (VLSIT), pp. 53–54, Jun 2012.

- [7] R. Bijesh *et al*, "Demonstration of In<sub>0.9</sub>Ga<sub>0.1</sub>As/GaAs<sub>0.18</sub>Sb<sub>0.82</sub> near broken-gap tunnel FET with I<sub>ON</sub>=740µA/µm, G<sub>M</sub>=700µS/µm and Gigahertz Switching Performance at V<sub>DS</sub>=0.5V", *IEDM Tech. Digest.*, pp. 28.2.1–28.2.4, Dec. 2013.

- [8] G. Zhou et al, "Novel gate-recessed vertical InAs/GaSb TFETs with record high I<sub>ON</sub> of 180µA/µm at V<sub>DS</sub>=0.5V," in *IEEE IEDM Tech. Dig.*, p.32.6.1–32.6.4, 2012.

- [9] K. Tomioka, M. Yoshimura, E. Nakai, F. Ishizaka, T. Fukui, "Integration of III-V nanowires on Si: from high-performance vertical FET to steep-slope switch," in IEEE IEDM Tech. Dig., pp.4.1.1–4.1.4, Dec. 2013.

- [10] R. Rooyackers et al, "A new complementary hetero-junction vertical Tunnel-FET integration scheme," IEDM Tech. Digest., pp. 4.2.1–4.2.4, Dec. 2013.

- [11] A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS Logic," in Proceedings of IEEE, vol. 98, iss. 12, pp. 2095-2110, Dec. 2010.

- [12] D. E. Nikonov et al, "Uniform methodology for benchmarking beyond-CMOS logic devices," in *IEEE IEDM Tech. Dig.*, p.25.4.1–25.4.4, 2012.

- [13] M. Luisier and G. Klimeck, "Performance comparisons of tunneling field-effect transistors made of InSb, carbon, and GaSb-InAs broken gap heterostructures," in IEEE IEDM Tech. Dig, pp.1,4, 2009.

- [14] nextnano3 next generation 3D nanodevice simulator (http://www.nextnano.de/nextnano3/), nextnano, 2008.

- [15] Mookerjea, S. et al, "On enhanced miller capacitance in interband tunnel transistors," in IEEE Elec. Dev. Lett., vol. 30, no.10, p. 1102–1104, Oct. 2009.

- [16] L. Zhang et al, "A compact model for double-gate tunneling field-effect-transistors and its implications on circuit behaviors," in IEEE IEDM Tech. Dig., pp. 6.8.1–6.8.4, Dec. 2012.

- [17] Alper, C.; De Michielis, L.; Dagtekin, N.; Lattanzio, L.; Ionescu, A.M., "Tunnel FET with non-uniform gate capacitance for improved device and circuit level performance," in Solid-State Device Research Conference (ESSDERC), 2012 Proceedings of the European, pp.161,164, Sep. 2012

- [18] Biswas, A.; Alper, C.; De Michielis, L.; Ionescu, A.M., "New tunnel-FET architecture with enhanced ION and improved Miller Effect for energy efficient switching," Device Research Conference (DRC), 2012 70th Annual, pp.131–132, June 2012

- [19] Yoonmyung Lee; Daeyeon Kim; Jin Cai; Lauer, I.; Chang, L.; Koester, S.J.; Blaauw, D.; Sylvester, D., "Low-Power Circuit Analysis and Design Based on Heterojunction Tunneling Transistors (HETTs)," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol.21, no.9, pp.1632– 1643, Sept. 2013

- [20] U. E. Avci et al, "Energy efficiency comparison of nanowire heterojunction TFET and Si MOSFET at Lg=13nm, including P-TFET and variation considerations," in IEDM Tech. Digest., pp. 33.4.1–33.4.4, Dec. 2013

- [21] Trivedi, Amit Ranjan; Carlo, Sergio; Mukhopadhyay, Saibal, "Exploring Tunnel-FET for ultra-low power analog applications: A case study on operational transconductance amplifier," Design Automation Conference (DAC), 2013 50th ACM / EDAC / IEEE, pp.1–6, May 2013.

- [22] Avci, U.E.; Rios, R.; Kuhn, K.; Young, I.A., "Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic," VLSI Technology (VLSIT), 2011 Symposium, pp.124,125, June 2011.