JFETIDG Model for Independent Dual-Gate JFETs 1.0.0

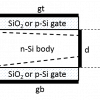

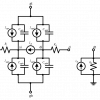

JFETIDG is a compact model for independent dual-gate JFETs. It is also applicable to: resistors with metal shields; the drift region of LDMOS transistors; the collector resistance of vertical bipolar transistors; and junctionless MOS transistors.

Listed in Compact Models

Additional materials available

Version 1.0.0 - published on 02 Apr 2017 doi:10.4231/D3TD9N91H - cite this Last public release: 1.0.3

Licensed under NEEDS Modified CMC License according to these terms

Description

JFETIDG is a compact model for independent dual-gate JFETs. It is applicable to devices with any combination of pn-junction and MOS gates, and is based on an exact solution for the channel conductance integrated along the device length. It includes modeling of the following effects:

- depletion pinching

- velocity saturation

- self-heating

- channel length modulation (CLM)

- drain-induced barrier lowering (DIBL)

- impact ionization

- mobility modulation

- parasitic currents, breakdown, and depletion and diffusion charge for pn-junction gates

- parasitic fixed capacitances for MOS gates

- local (single device) and global (W and L dependent) geometry models

- temperature dependence

- noise

- statistical variation

- parameterization in terms of both physical (doping, layer thicknesses, mobility) and phenomenological (depletion pinching, sheet resistance) quantities

Model Release Components ( Show bundle contents ) Bundle

JFETIDG Model for Independent Dual-Gate JFETs 1.0.0 Verilog-A(ZIP | 29 KB)

JFETIDG Model for Independent Dual-Gate JFETs 1.0.0 Benchmarks(ZIP | 662 KB)

JFETIDG Model for Independent Dual-Gate JFETs 1.0.0 Parameters(VAR/WWW/NANOHUB/APP/SITE/PUBLICATIONS/00173/00192/LAD7V906YB/PARAMETERS/PARAMETERSETS | 522 B )

JFETIDG Model for Independent Dual-Gate JFETs 1.0.0 Manual(GZ | 160 KB)

2016TED_JFETIDGpartI.pdf(PDF | 2 MB)

2016TED_JFETIDGpartII.pdf(PDF | 3 MB)

- License terms

Key References

K. Xia, C. C. McAndrew, and B. Grote, “Dual-gate JFET modeling I: Generalization to include MOS gates and efficient method to calculate drain-source saturation voltage,” IEEE Trans. Electron Dev., vol. 63, no. 4, pp. 1408-1415, Apr. 2016.

K. Xia, C. C. McAndrew, and B. Grote, “Dual-gate JFET modeling II: Source pinch-off voltage and complete Ids modeling formalism,” IEEE Trans. Electron Dev., vol. 63, no. 4, pp. 1416-1422, Apr. 2016.

Cite this work

Researchers should cite this work as follows:

- McAndrew, C.; Xia, K. (2017). JFETIDG Model for Independent Dual-Gate JFETs. nanoHUB. doi:10.4231/D3TD9N91H

Notes

This is the first release of the model. It has been tested on measured and TCAD data from dual-gate JFETs, on resistors with metal shields, on junctionless MOS transistor data, and in conjunction with PSP as a model for LDMOS transistors.