Dragica Vasileska

## nanoHUB Used in Research: A One Developer/User View

# **Talk Outline**

- Introduction: PUNCH and nanoHUB

- Moore's Law for Transistor Scaling: SCHRED Tool

- Diving Deeper into Quantum Mechanics: QUAMC2D

- Nanoelectronics: The Need for NEMO5

- What nanoHUB Tools Can/Can't Do

- Conclusions

# nanoHUB Predecessor: PUNCH

# PUNCH: Purdue University Network Computing Hub

| Developed at: | Purdue University               |

|---------------|---------------------------------|

| Deployed:     | 1995                            |

| Retired:      | April, 2007                     |

| Usage:        | 4600 users, 395,000 simulations |

# Prof. Vasileska became affiliated to PUNCH as part of a NSF sponsored **DESCARTES** project in 1998:

- SCHRED MOS Capacitor Tool: installed on PUNCH 1998 (Dragica Vasileska)

- SCHRED Dual-Gate Capacitor Tool: installed on PUNCH 1999 (Dragica Vasileska and Zhibin Ren)

### NCN nanoHUB Launched 2002

# **Dragica Vasileska Contributions**

| Item                                  | Value                                                  |

|---------------------------------------|--------------------------------------------------------|

| Contributions:                        | 372                                                    |

| <b>Total Simulation Users Served:</b> | 22,144                                                 |

| Rank by Contributions:                | 3 / 1588                                               |

| First Contribution:                   | 09 Mar 2005                                            |

| Last Contribution:                    | 17 Feb 2015                                            |

| <b>Citations on Contributions:</b>    | 136                                                    |

| Usage in Courses/Classrooms:          | 7,516 users served in 480 courses from 47 institutions |

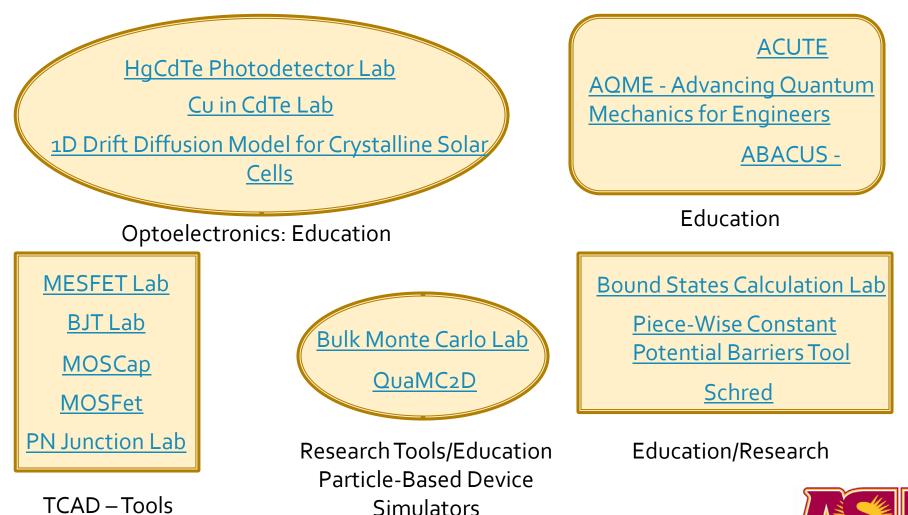

## Tools Co-Authored by Vasileska: 19

Education

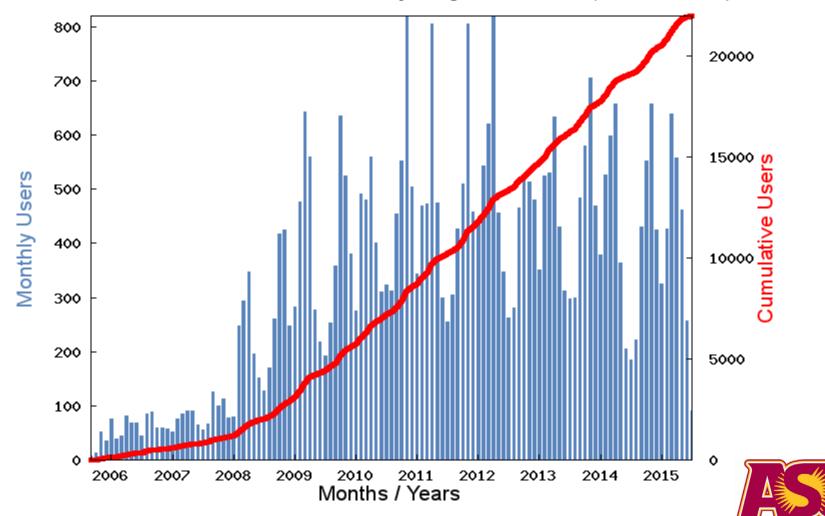

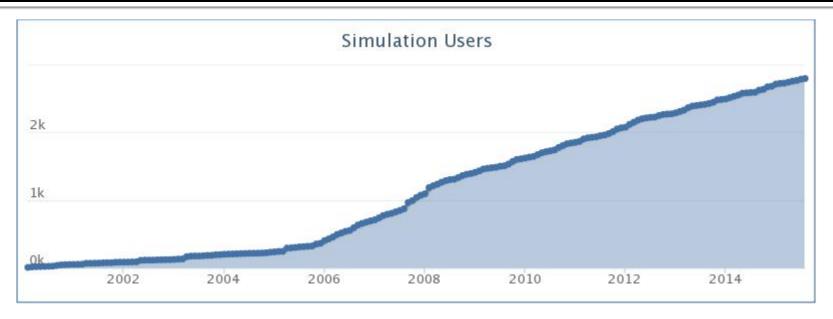

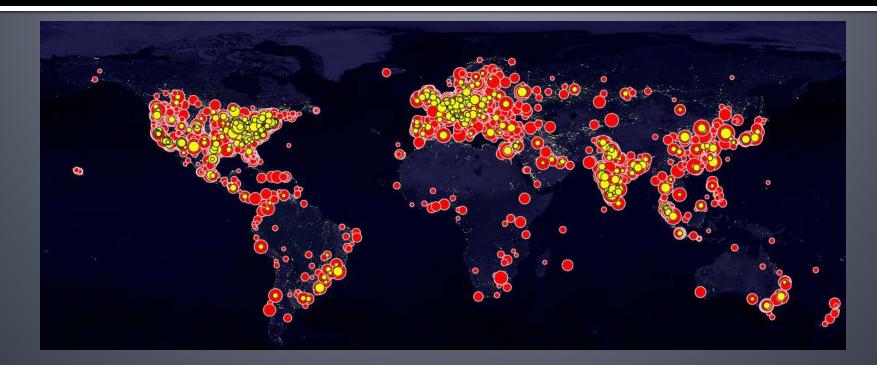

# Impact Graph

Users of Simulation Tools Authored by Dragica Vasileska (21,957 Users)

# **Tool-Based Curricula**

New paradigms of learning are necessary for training students in the vibrant and constantly changing field of **nanoelectronics**.

# Prof. Vasileska and Prof. Klimeck propose a novel methodology: Tool-Based Curricula.

**Tool-Based Curricula** consists of assembling a set of computational simulation tools with:

- demos on how to use the tools,

- the objectives of the tool and what can be learned with them,

- assembly of solved problems,

- homework assignments,

- challenge problems which are related to real world applications.

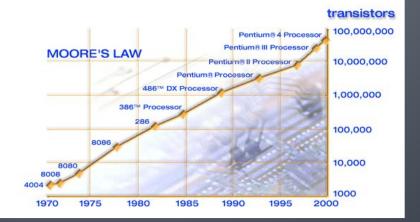

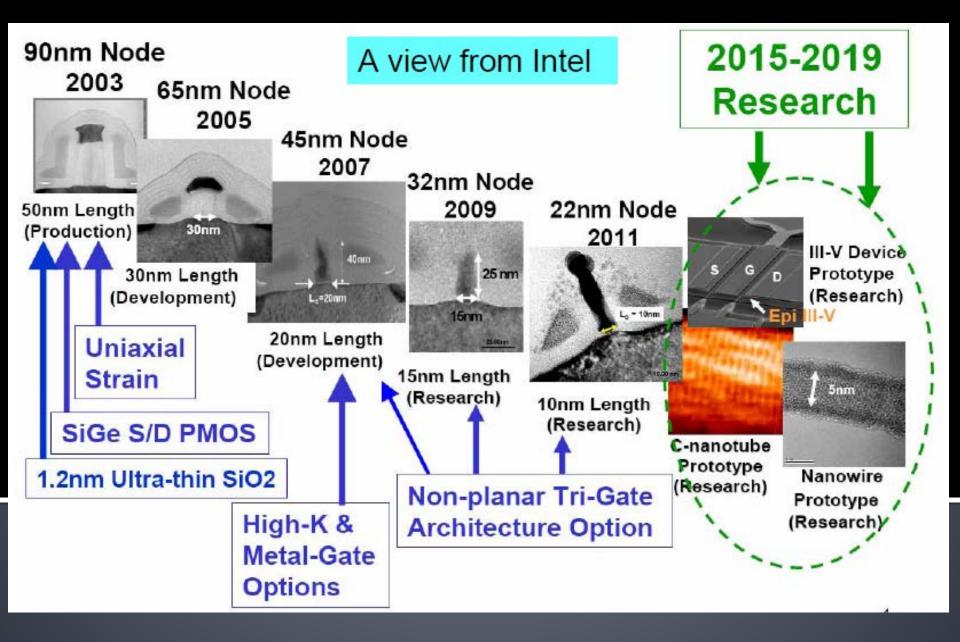

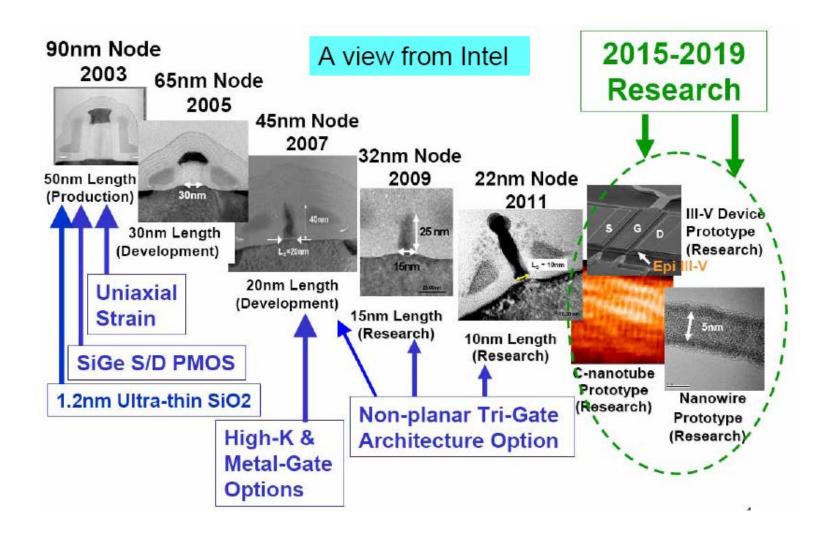

# Moore's Law for Transistor Scaling: NEED for SCHRED Tool

Gordon Moore "every 1.5 years complexity doubles"

# **Quantum Mechanical Size Quantization**

#### **Historical Perspective**

- Bacarani and Worderman ⇒ transconductance degradation (Proceedings of the IEDM, pp. 278-281, 1982)

- Hartstein and Albert  $\Rightarrow$  estimate of the inversion layer thickness (Phys. Rev. B, Vol. 38, pp.1235-1240, 1988)

- van Dort et al. ⇒ analytical model for Vth which accounts for QM effects (IEEE TED, Vol. 39, pp. 932-938, 1992)

- Takagi and Toriumi  $\Rightarrow$  physical origins of Cinv (IEEE TED, Vol. 42, pp. 2125-2130, 1995)

- Hareland et al.  $\Rightarrow$  modeling of the QM effects in the channel (IEEETED, Vol. 43, pp. 90-96, 1996)

- Krisch et al.  $\Rightarrow$  poly-gate capacitance attenuation (IEEE EDL, Vol. 17, pp. 521-524, 1996)

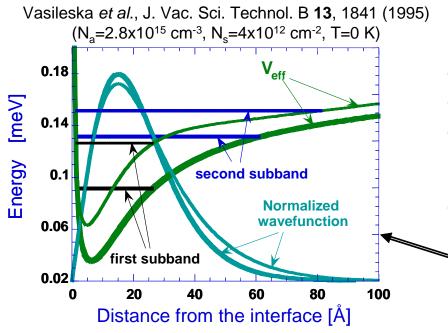

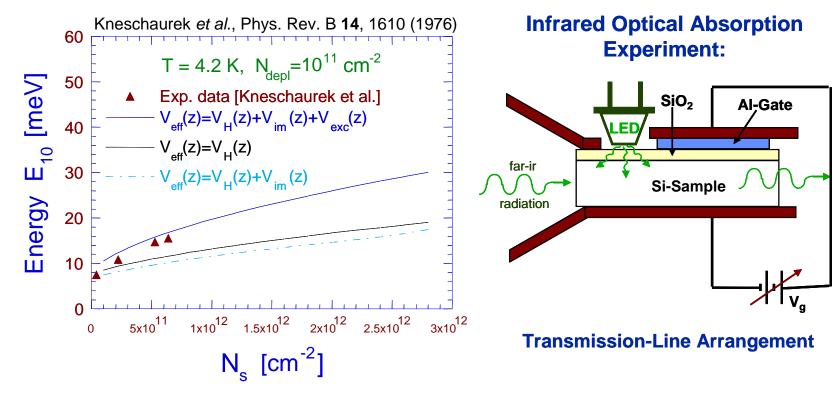

- Vasileska, Schroder and Ferry  $\Rightarrow$  influence of many-body effects on Cinv (IEEE TED, Vol. 44, pp. 584-587, 1997)

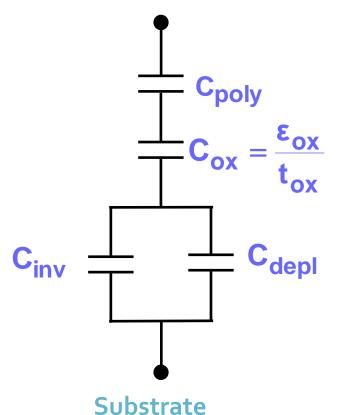

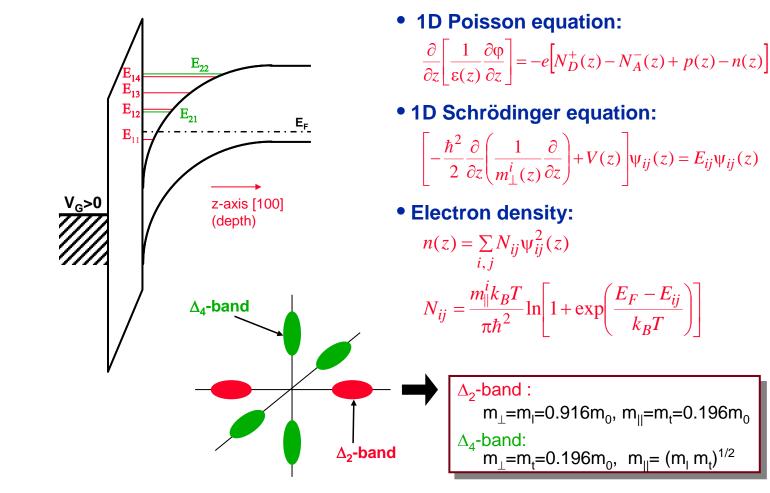

# **Quantum-Mechanical Size Quantization**

### **Physical Origin**

Gate

D. Vasileska, and D.K. Ferry, "The influence of poly-silicon gates on the threshold voltage, inversion layer and total gate capacitance in scaled Si-MOSFETs," *Nanotechnology* Vol. 10, pp.192-197 (1999).

# Quantum-Mechanical Size Quantization

### **Numerical Modeling**

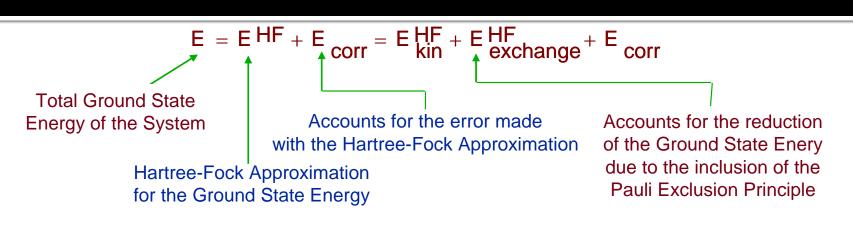

# **Exchange-Correlation**

#### **Exchange-Correlation Correction:**

- Lower subband energies

- i Increase in the subband separation

- i Increase in the carrier concentration at which the Fermi level crosses into the second subband

- Contracted wavefunctions

- Thick (thin) lines correspond to the case when the exchange-correlation corrections are included (omitted) in the simulations.

# **Comparison With Experiments**

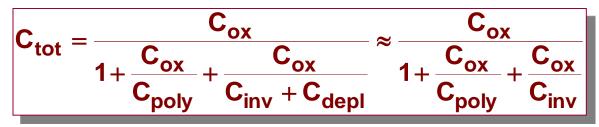

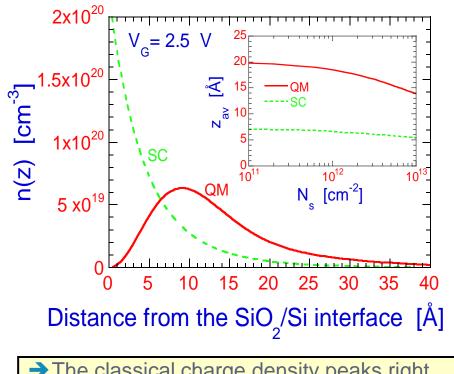

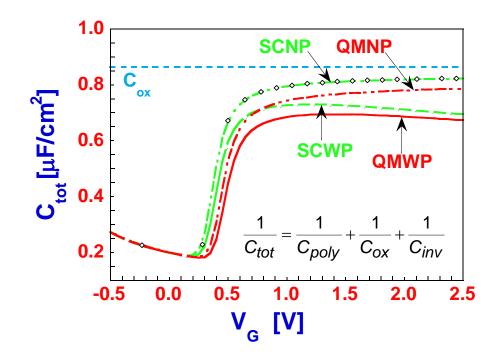

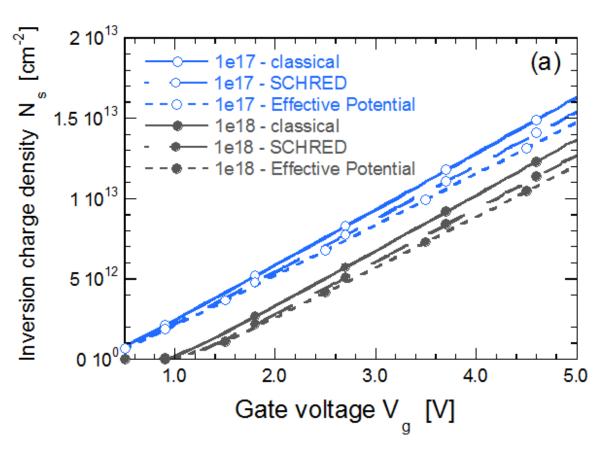

# Simulation Results Obtained With SCHRED

- The classical charge density peaks right at the SC/oxide interface.

- The quantum-mechanically calculated charge density peaks at a finite distance from the SC/oxide interface, which leads to larger average displacement of electrons from that interface.

$\rightarrow$  C<sub>inv</sub> reduces C<sub>tot</sub> by about 10%

$\rightarrow$  C<sub>poly</sub>+ C<sub>inv</sub> reduce C<sub>tot</sub> by about 20%

→ With poly-depletion C<sub>tot</sub> has pronounced gate-voltage dependence

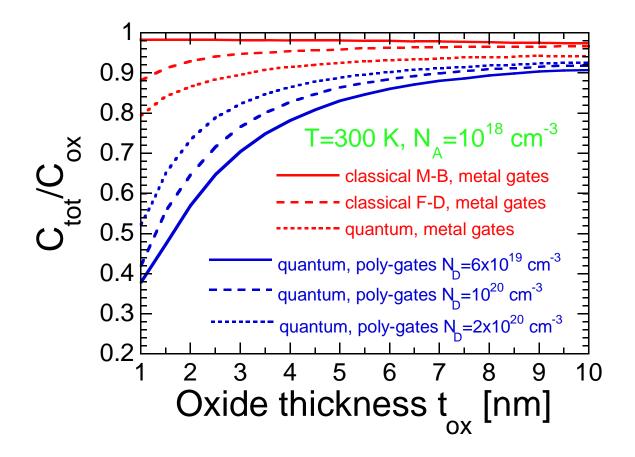

# Simulation Results Obtained With SCHRED

**Degradation of the Total Gate Capacitance C**<sub>tot</sub> **for Different Device Technologies**

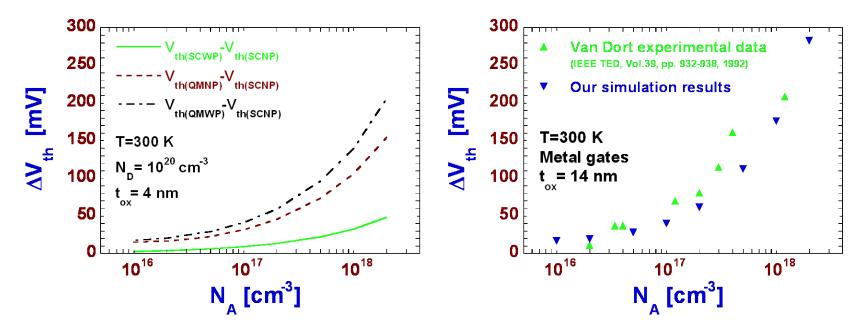

# Simulation Results Obtained With SCHRED

MOS Capacitor with both Metal and Poly-Silicon Gates

- There is close agreement between the experimentally derived threshold voltage shift and our simulation results

# SCHRED Users Since Its Posting – 120 Citations

It is evident that many years of research by a great many people, both before and after the discovery of the transistor effect, has been required to bring our knowledge of semiconductors to its present development. We were fortunate to be involved at a particularly opportune time and to add another small step in the control of Nature for the benefit of mankind.

- John Bardeen, 1956 Nobel lecture

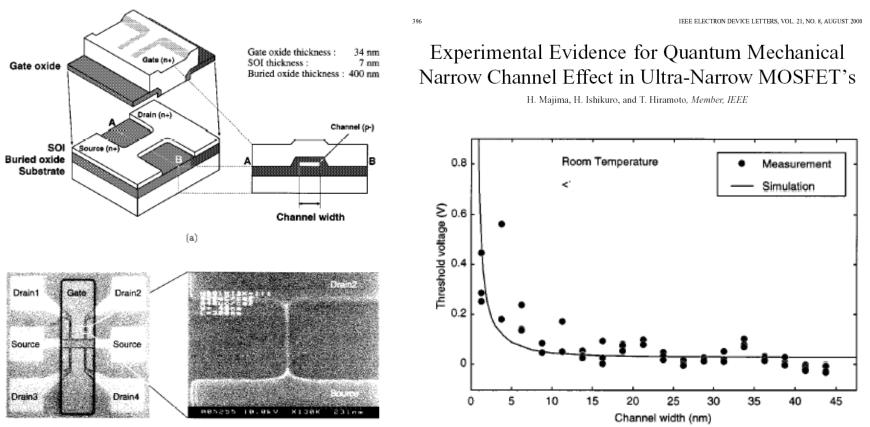

# Diving Deeper into Quantum Mechanics: QUAMC2D

## More Moore ...

# Welcome to the SOI World!

#### <u>Highlights</u>

- Reduced junction capacitance.

- Absence of latchup.

- Ease in scaling (buried oxide need not be scaled).

- Compatible with conventional Silicon processing.

- Sometimes requires fewer steps to fabricate.

- Reduced leakage.

- Improvement in the soft error rate.

#### <u>Drawbacks</u>

- Drain Current Overshoot.

- Kink effect

- Thickness control (fully depleted operation).

- Surface states.

### Incorporation of Quantum-Mechanical Size-Quantization Effects Mandatory

#### Quantum correction methods

- Drift-diffusion + hydrodynamic models

- Analytical corrections

- Hansch method

- Van Dort method

- Numerical approaches

- Density gradient method

- Particle-based device simulators

- Effective Potential Approach in Conjunction With Particle-Based Approaches

- Solution of the Schrodinger-Transport-Poisson Problem

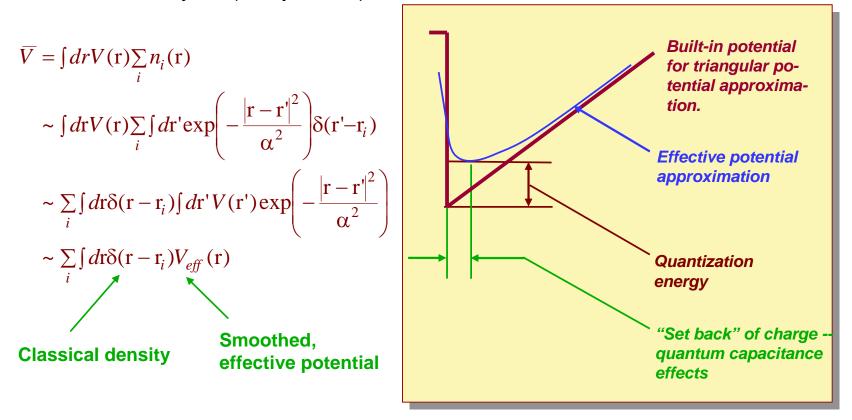

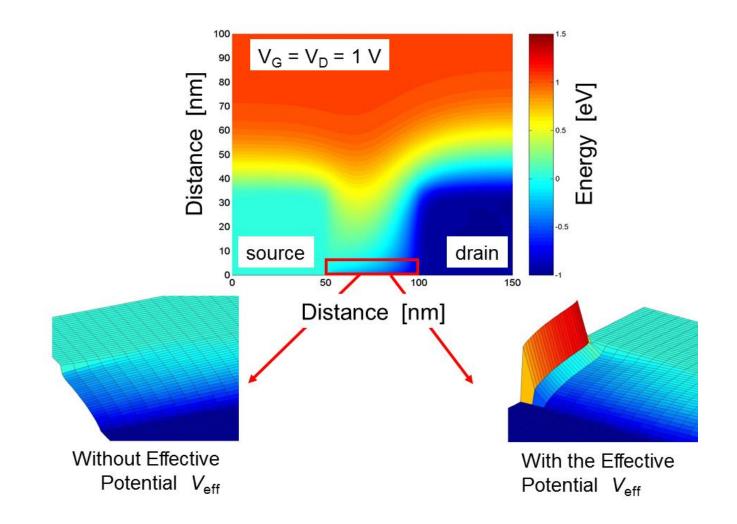

# **Effective Potential Approach**

In principle, the effective role of the potential can be rewritten in terms of the non-local density as (Ferry *et al.*<sup>1</sup>):

<sup>1</sup> D. K. Ferry, Superlatt. Microstruc. 27, 59 (2000);

# **Comparison to 1D-SP**

The Gaussian fitting parameter  $a_0 = 0.5$  nm.

# Simulation of a Conventional MOSFET

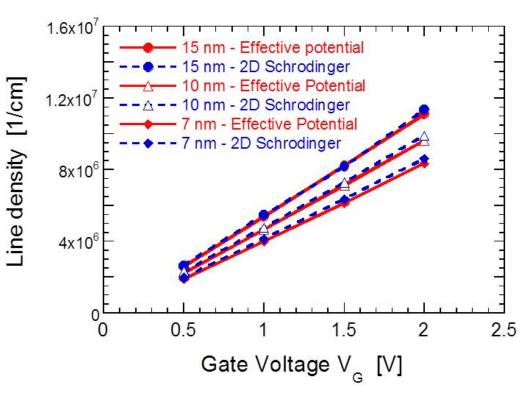

# **Comparison to 2D-SP**

**Method Validation!**

Excellent agreement is observed between the two approaches when using the theoretical value for the Gaussian smoothing parameter of 0.64 nm.

# Application of the Effective Potential Approach and QUAMC<sub>3</sub>D

# Drawbacks of the Effective Potential Approach

- Does not calculate the subband structure

- Does not calculate the 1D/2D density of states in nanowires/inversion layers

- ➔ Scattering is not treated accurately

# Nanoelectronics: The Need for NEMO5

# Towards Nanotransistors: More Moore ... & More Than Moore

Intel's next technology node is a 14 nm FinFET.

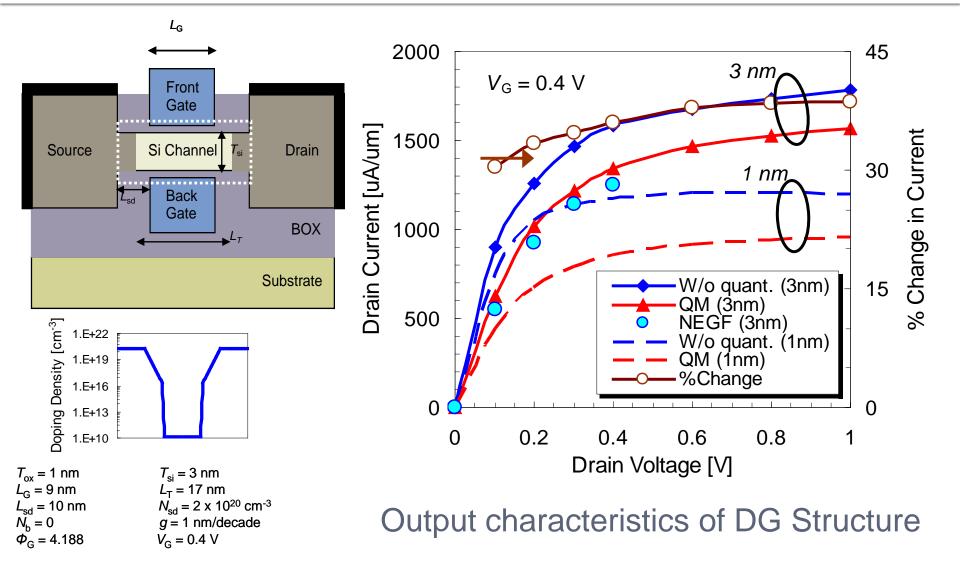

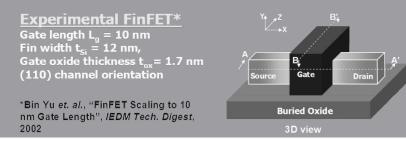

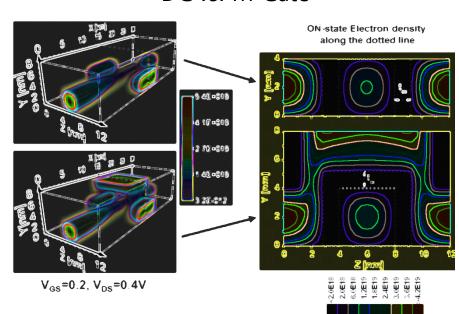

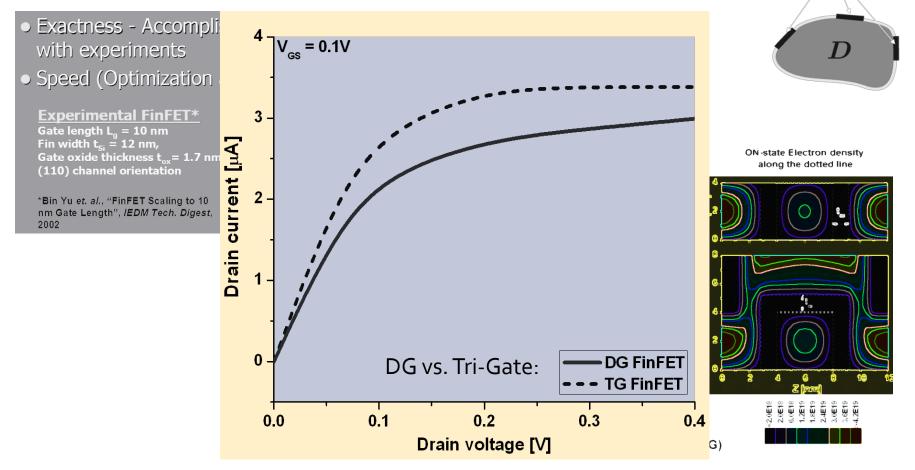

### Ballistic Modeling of FinFET Device with Contact Block Reduction (CBR) Method

### D. Mamaluy, H. R. Khan, D. Vasileska

- Exactness Accomplished with comparison with experiments

- Speed (Optimization and Process Variation)

H. R. Khan, D. Mamaluy and D. Vasileska, "Quantum transport simulation of experimentally fabricated nano-FinFET", *IEEE Trans. Electron Devices*, Vol. 54 (4), pp. 784-796 (2007).

H. R. Khan, D. Mamaluy and D. Vasileska, "Approaching Optimal Characteristics of 10 nm High Performance Devices" a Quantum Transport Simulation Study of Si FinFET, *IEEE Trans. Electron Devices*, Vol. 55(1), pp. 743-753 (2008).

Properties of a GOOD Device simulator

DG vs. Tri-Gate

# Ballistic Modeling of FinFET Device with CBR Method

### D. Mamaluy, H. R. Khan, D. Vasileska

H. R. Khan, D. Mamaluy and D. Vasileska, IEEE Transactions Electron Dev. Vol. 55(8), pp. 2134 – 2141, August 2008.

# **Complexity of Methods**

| Method                                                 | Computational cost                                                                                                                      |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Transfer matrix + QTBM                                 | $N_{E} \times O\left(N_{TOTAL}^{3}\right)$                                                                                              |

| NanoMOS (Purdue University)                            | $N_{E} \times N_{x} \times O\left(\left[N_{y}N_{z}\right]^{2}\right) \approx N_{E} \times O\left(N_{\text{Total}}^{\frac{5}{3}}\right)$ |

| QDAME (IBM, S. Laux)                                   | $N_{\textit{total}} \times O\left(N_{\textit{eigen}}^2\right) + N_E \times O\left(N_{\textit{total}}^{\frac{3}{2}}\right)$              |

| CBR                                                    | $N_{\textit{total}} \times O\left(N_{\textit{eigen}}^2\right) + N_E \times O\left(N_{\textit{total}}\right)$                            |

| Notations                                              |                                                                                                                                         |

| $N_E$ : number of energy steps;                        |                                                                                                                                         |

| $N_{TOTAL}$ : number of grid points                    | <b>CBR WINS !!!</b>                                                                                                                     |

| $N_{\scriptscriptstyle eigen}$ : number of eigenvalues |                                                                                                                                         |

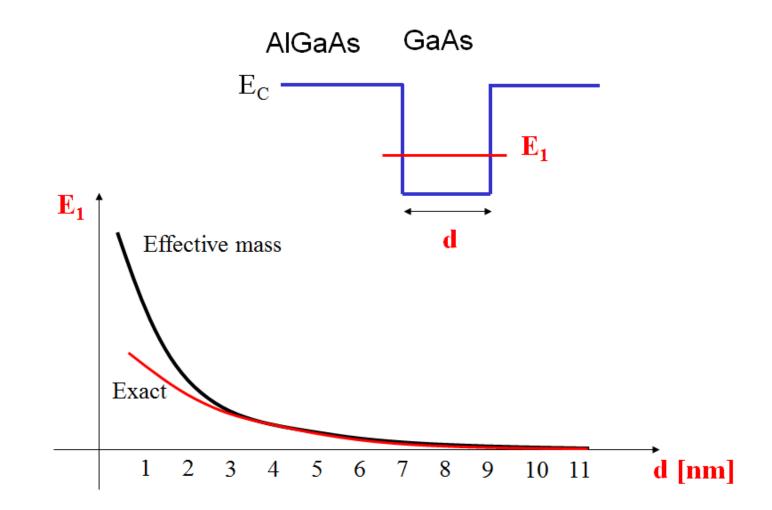

# How good is effective mass approximation?

A. Di Carlo, private communication.

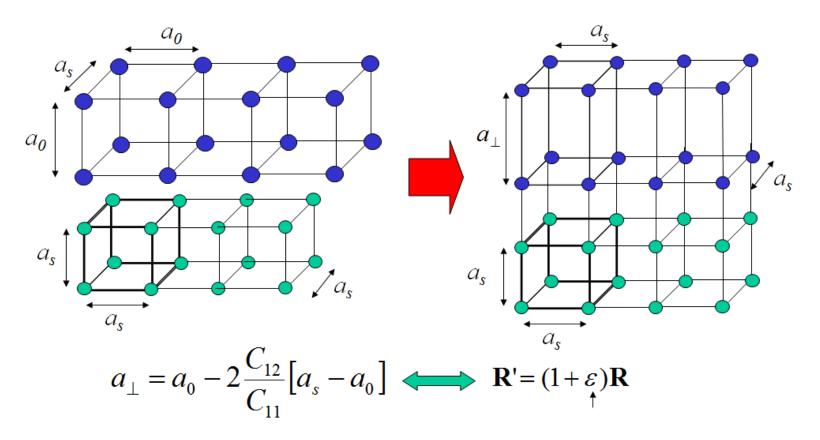

## Strain

An epitaxial layer is grown, on a substrate with different lattice constant. The epilayer deforms (strain)

A. Di Carlo, private communication.

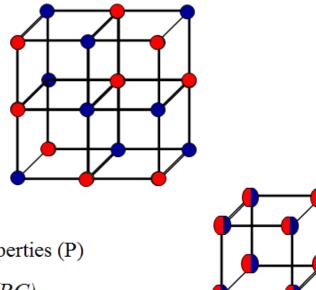

# **Disorder - Alloys**

Usually, tight-binding parameterizations are made for single elments and binary compounds (Si, Ge, GaAs, InAs etc.). However, nanostructure are usually build by using also ternary (AlGaAs etc.) and quatrary (InGaAsP etc.) alloys.

1) Supercell calculations

$A_{0.5}B_{0.5}C$

Average over an ensamble of configurations

2) Virtual crystal approximation

A new crystal is defined with averaged properties (P)

$P(A_x B_{1-x} C) = x P(AC) + (1-x) P(BC)$

3) Other methods (Modified VCA, CPA, T-matrix etc.)

A. Di Carlo, private communication.

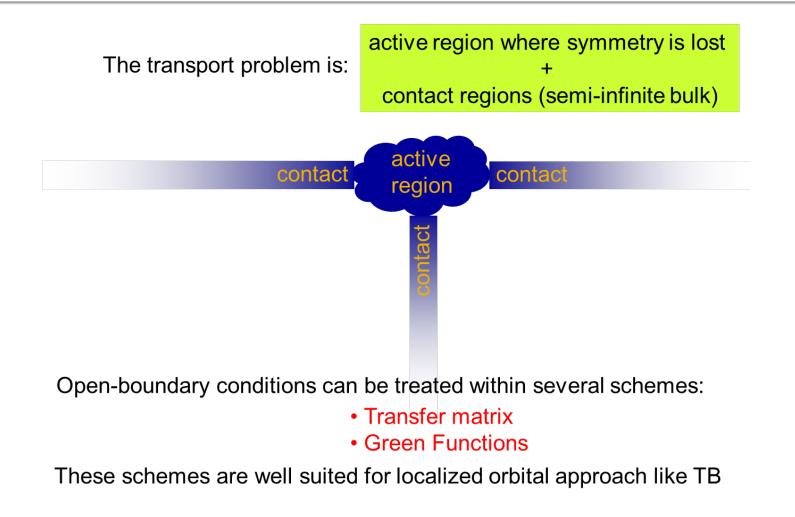

## **Boundary Conditions for Transport**

A. Di Carlo, Private Communication.

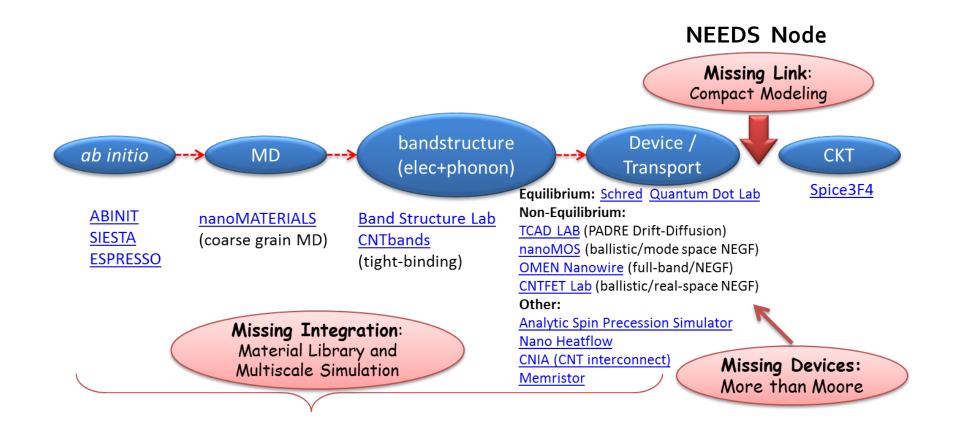

## NEMO5: The Nanoelectronics Tool

NEMO<sub>5</sub> is the fifth edition of the NanoElectronics MOdeling Tools of the iNEMO group. It incorporates the core concepts and insights gained from 15 years of development of NEMO-1D, NEMO-3D, NEMO-3D-Peta and OMEN.

The core capabilities of NEMO<sub>5</sub> lie in the atomic-resolution calculation of nanostructure properties:

strain relaxation, phonon modes, electronic structure using the tightbinding model, self-consistent Schroedinger-Poisson calculations, and quantum transport.

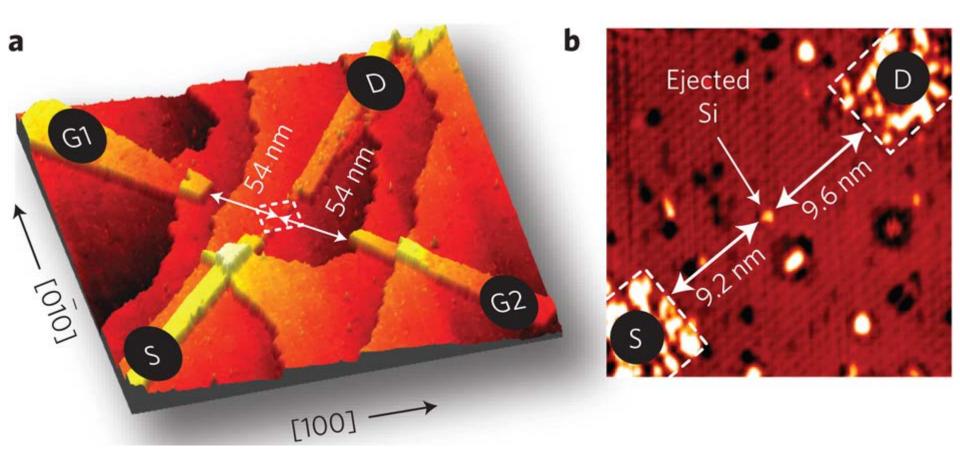

## A representative Example: Single Atom Transistor

Martin Fuechsle, Jill A. Miwa, Suddhasatta Mahapatra, Hoon Ryu, Sunhee Lee, Oliver Warschkow, Lloyd C. L. Hollenberg, Gerhard Klimeck & Michelle Y. Simmons, Nature Nanotechnology 7, 242–246 (2012) doi:10.1038/nnano.2012.21

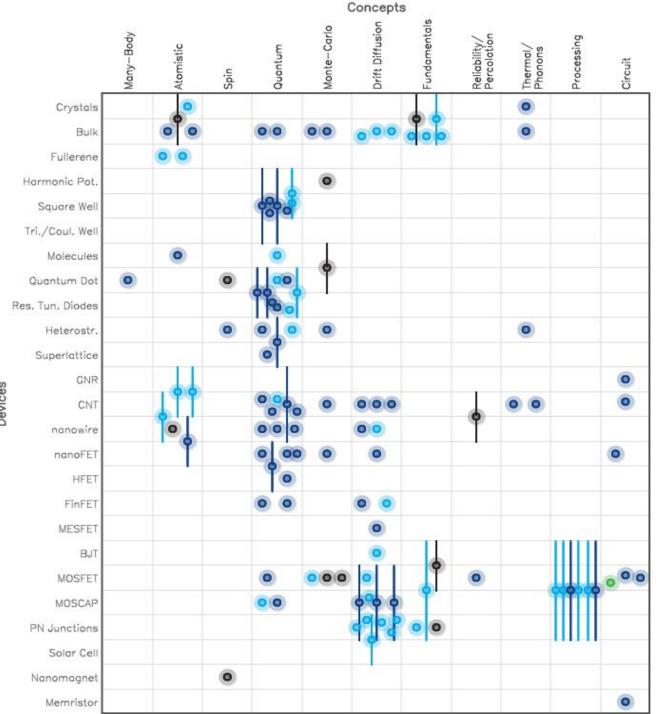

# What nanoHUB Tools Can and Can't Do

A One Person's View

Devices

# What nanoHUB Can /Can't Do

## **Can't Do Random Dopant Fluctuations**

#### **Random Dopants**

all transistors are similar because of *self averaging*

## **Experimental Evidence of RDF**

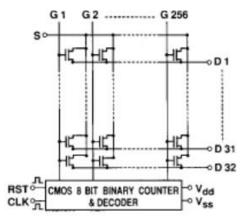

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 41, NO. 11, NOVEMBER 1994

Experimental Study of Threshold Voltage Fluctuation Due to Statistical Variation of Channel Dopant Number in MOSFET's

Tomohisa Mizuno, Member, IEEE, Jun-ichi Okamura, Member, IEEE, and Akira Toriumi, Member, IEEE

Fig. 1. New test structure which consists of the 8 k-NMOSFET array and the CMOS peripheral circuits (the CMOS counter and the CMOS decoders). RST and CLK show the reset and the clock terminals, respectively. (Reprinted from: T. Mizuno, J. Okamura, and A. Toriumi, "Experimental Study of Threshold Voltage Fluctuations Using an 8K MOSFET's Array," Technical Papers of Symposium on VLSI Technology, Kyoto, Japan, p. 41, 1993.)

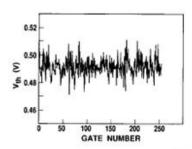

Fig. 4. Threshold voltage versus the gate number in 256 NMOSFET's, where  $L_{el} = 0.5 \ \mu m$ ,  $T_{ox} = 11 nm$ , and  $\overline{N}_a = 7.1 \times 10^{16} \text{ cm}^{-3}$ . (Reprinted from: T. Mizuno, J. Okamura, and A. Toriumi, "Experimental Study of Threshold Voltage Fluctuations Using an 8K MOSFET's Array," Technical Papers of Symposium on VLSI Technology. Kyoto, Japan. p. 41, 1993.)

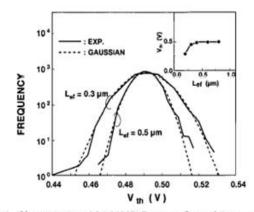

Fig. 6.  $V_{\rm th}$  distribution of 8 k-MOSFET array at  $L_{\rm ef} = 0.5 \ \mu {\rm m}$  and 0.3  $\mu {\rm m}$ , where  $T_{\rm ex} = 11 \ {\rm nm}$  and  $\overline{N}_a = 7.1 \times 10^{16} \ {\rm cm}^{-3}$ . The vertical axis shows the frequency. The solid and the dashed lines show the experimental data and the calculated Gaussian distribution, respectively. The inset shows  $V_{\rm th}$  as a function of  $L_{\rm ef}$ .

## **Unintentional Dopants?**

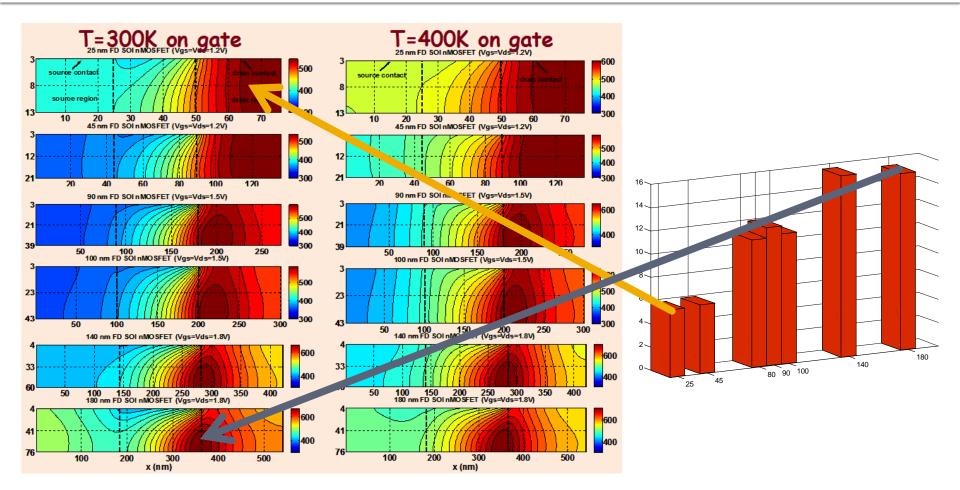

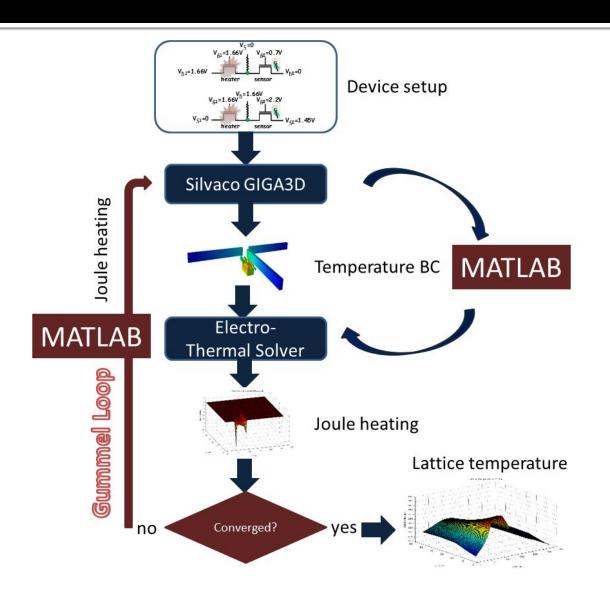

# Can't Do Self-Heating at the Device Level

K. Raleva, D. Vasileska, S. M. Goodnick and M. Nedjalkov, Modeling Thermal Effects in Nanodevices, IEEE Transactions on Electron Devices, vol. 55, issue 6, pp. 1306-1316, June 2008

## **Multi-Scale Simulations**

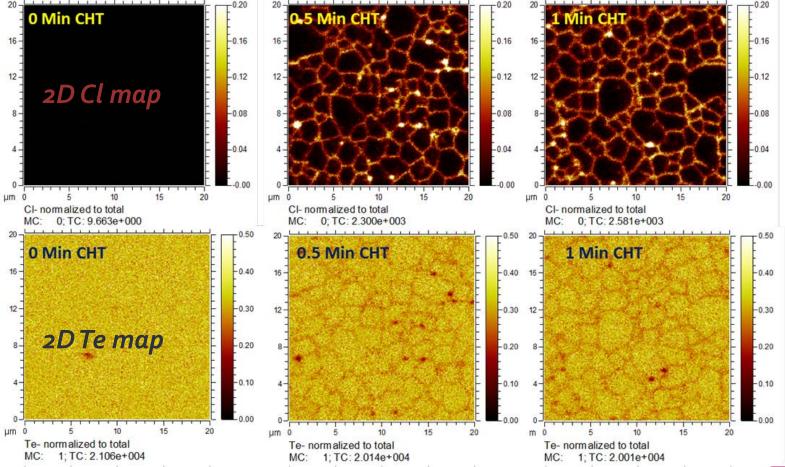

# **Optoelectronics? What are we missing?**

# Conclusions

One picture is worth a million words!

Over 300,000 users annually!!!