**Solid State Devices**

# Section 31 MOSFET Non-Idealities

**Gerhard Klimeck**

gekco@purdue.edu

School of Electrical and Computer Engineering

### Section 31 MOSFET Non-Idealities

|                   | Equilibrium | DC | Small<br>signal | Large<br>Signal | Circuits |

|-------------------|-------------|----|-----------------|-----------------|----------|

| PN<br>Diode       |             |    |                 |                 |          |

| Schottky<br>Diode |             |    |                 |                 |          |

| BJT/<br>HBT       |             |    |                 |                 |          |

| MOScap<br>MOSFET  |             |    |                 |                 |          |

# Section 31 MOSFET Non-Idealities

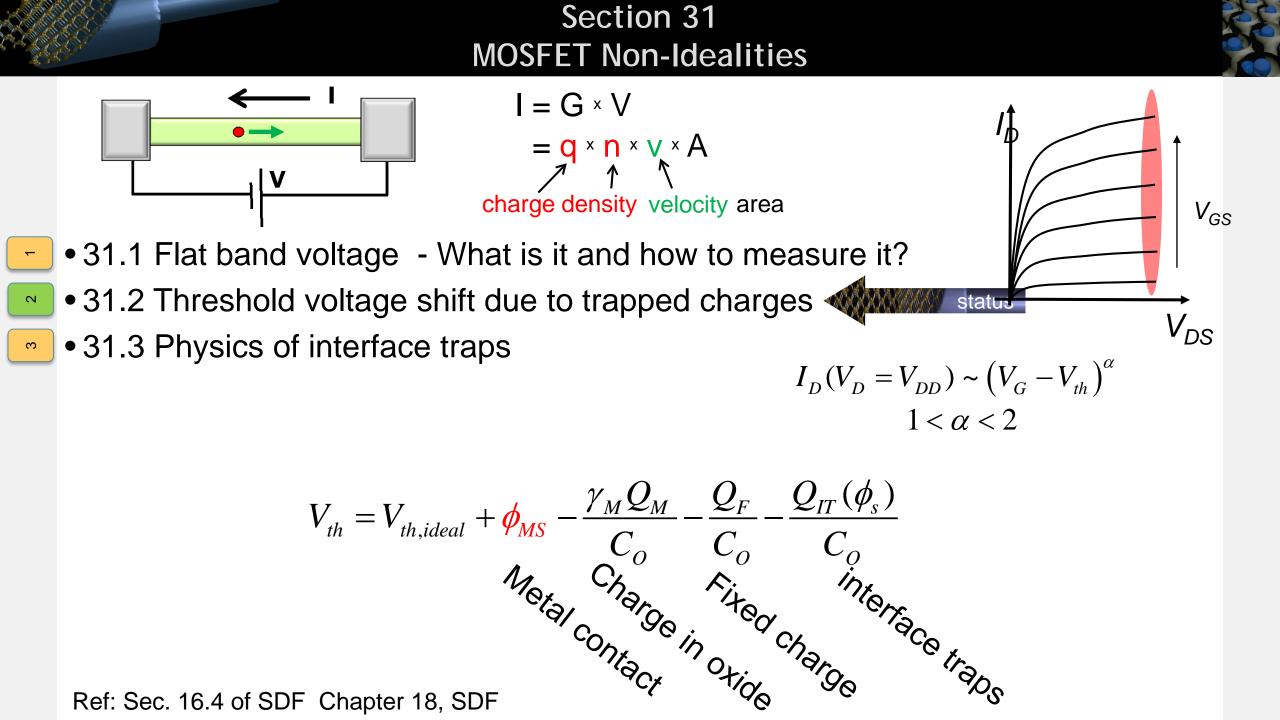

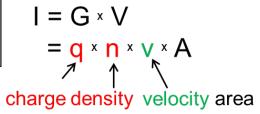

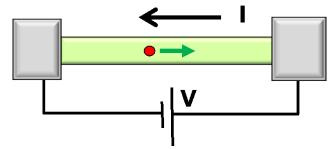

$I = G \times V$ = q × n × v × A  $\checkmark$ charge density velocity area

- 31.1 Flat band voltage What is it and how to measure it?

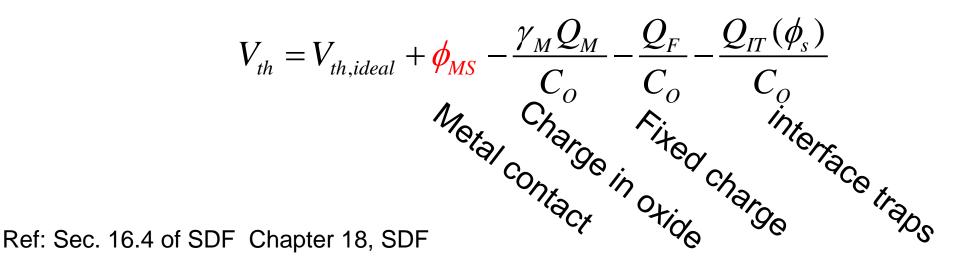

- 31.2 Threshold voltage shift due to trapped charges

- 31.3 Physics of interface traps

2

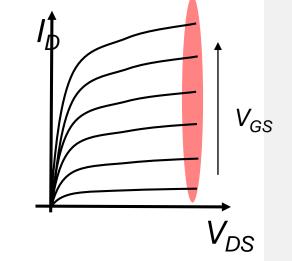

$$I_D(V_D = V_{DD}) \sim (V_G - V_{th})^{\alpha}$$

$$1 < \alpha < 2$$

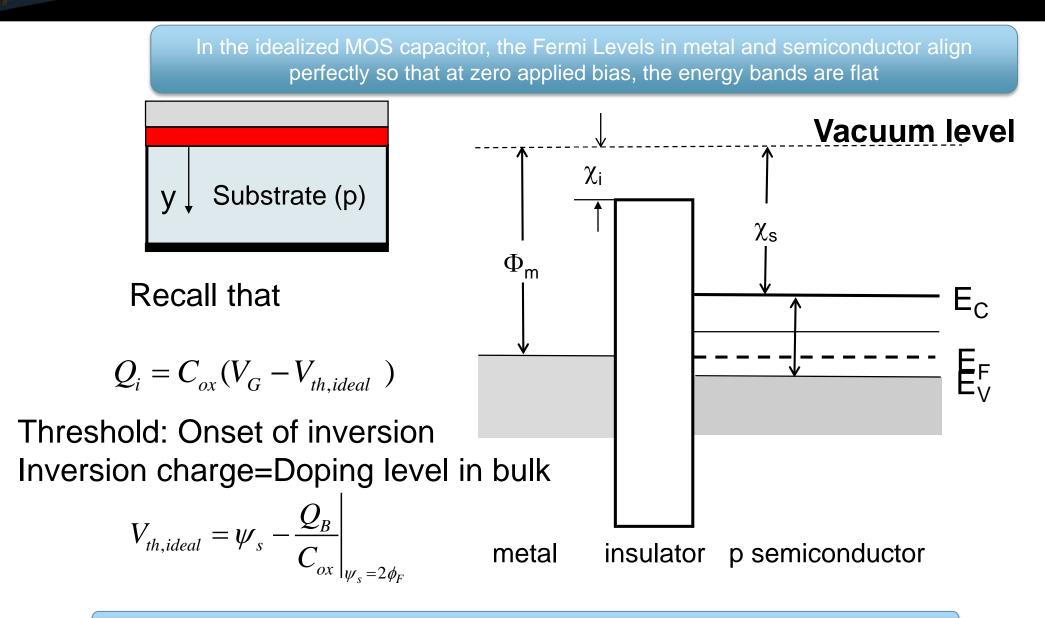

# (1) Idealized MOS Capacitor

In historical perspective: Aluminum => poly => back to metals

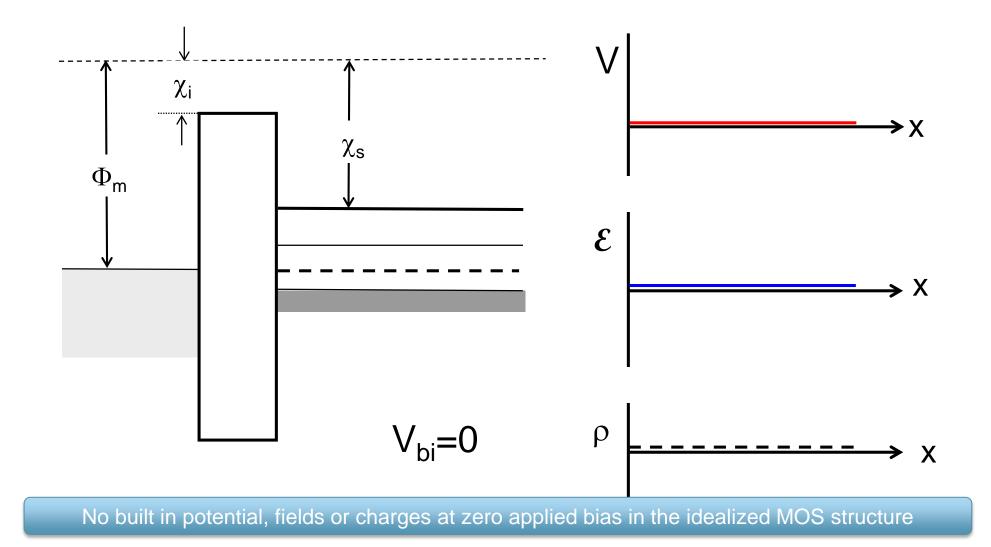

Potential, Field, Charges

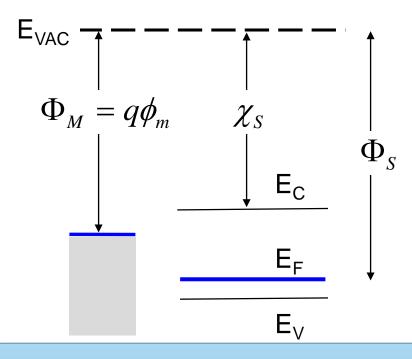

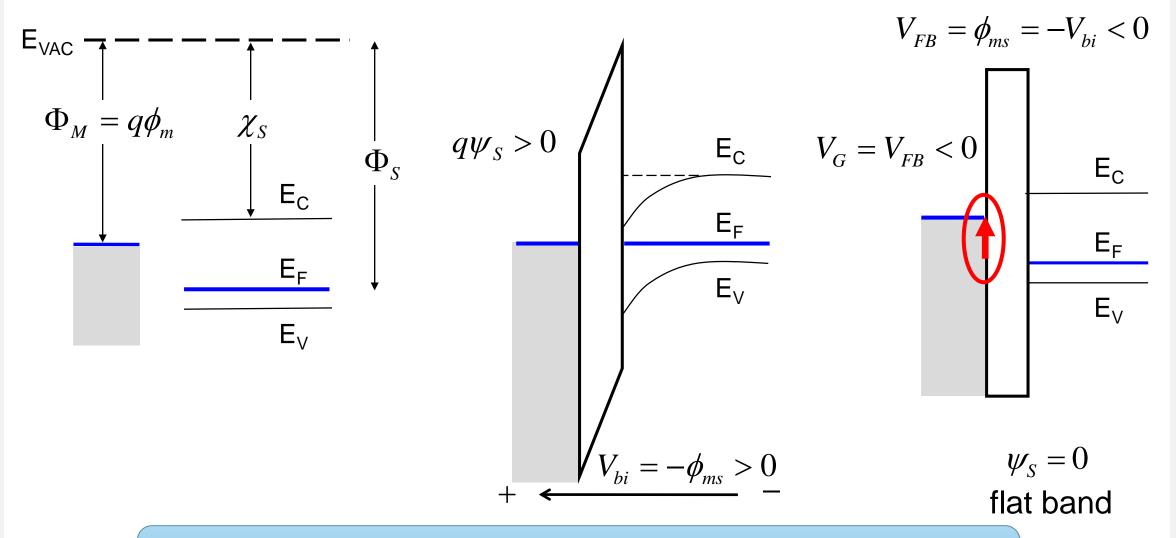

Real MOS Capacitor with  $\Phi_{M} < \Phi_{S}$

#### Note the difference

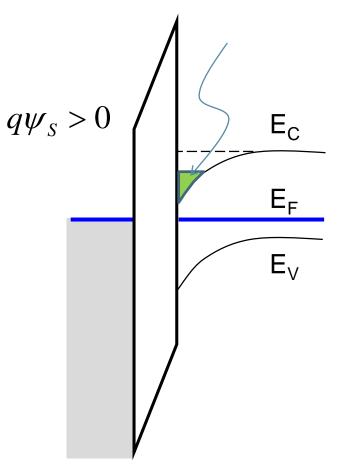

In reality, the metal and semiconductor Fermi Levels are never aligned perfectly → when you bring them together there is charge transfer from the bulk of the semiconductor to the surface so that we have alignment

Do we need to apply less or more  $V_G$  to invert the channel?

# Real MOS Capacitor with $\Phi_{M} < \Phi_{S}$ in Flatband Condition

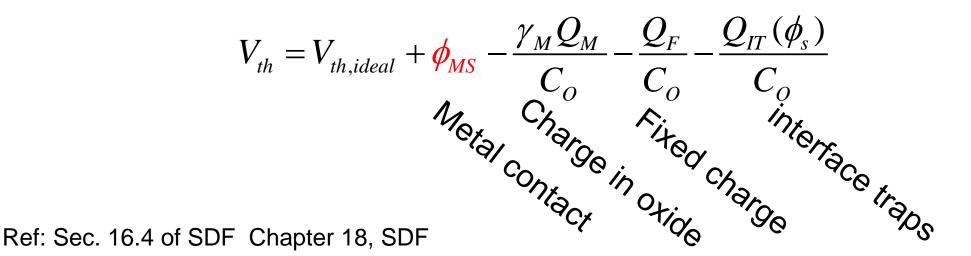

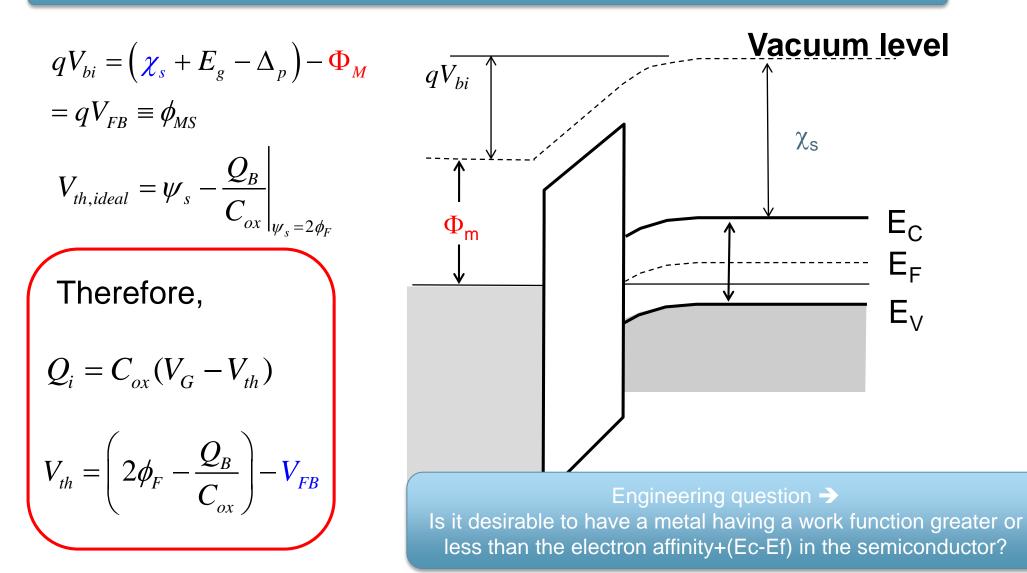

The Flatband Voltage is the voltage applied to the gate that gives zero-band bending in the MOS structure. Applying this voltage nullifies the effect of the built-in potential. This voltage needs to be incorporated into the idealized MOS analysis while calculating threshold voltage

#### How to Calculate Built-in or Flat-band Voltage

The presence of a flatband voltage lowers or raises the threshold voltage of a MOS structure.

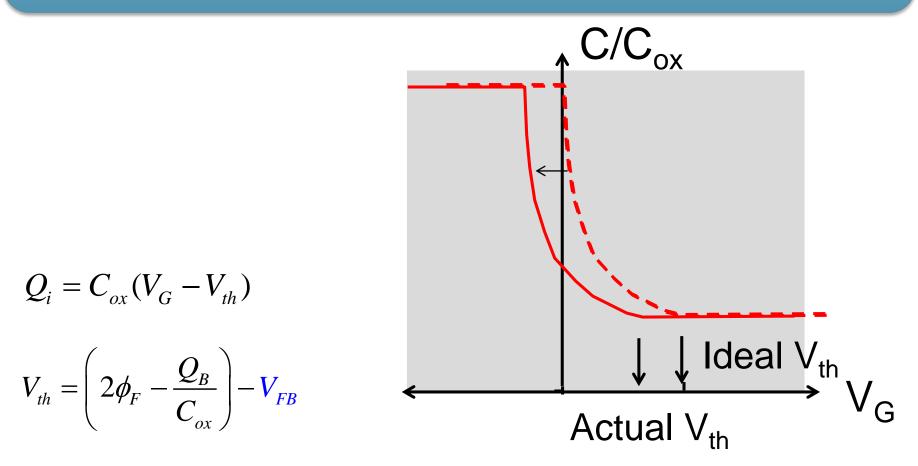

# Measure of Flat-band shift from C-V Characteristics

The transition point between accumulation and depletion in a non-ideal MOS structure is shifted to the left when the metal work function is smaller that the electron affinity +(Ec-Ef). At **zero applied bias the semiconductor is already depleted** so that a very small positive bias inverts the channel. The flatband voltage is the amount of voltage required to shift the curve such that the transition point is at zero bias.

# Section 31 MOSFET Non-Idealities

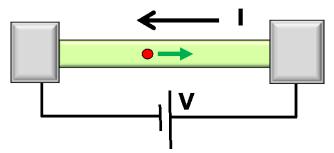

$V_{GS}$

$V_{DS}$

status

$I = G \times V$ = q × n × v × A  $\checkmark$   $\uparrow$   $\checkmark$ charge density velocity area

- 31.1 Flat band voltage What is it and how to measure it?

- 31.2 Threshold voltage shift due to trapped charges

- 31.3 Physics of interface traps

$$I_D(V_D = V_{DD}) \sim (V_G - V_{th})^{\alpha}$$

$$1 < \alpha < 2$$