Spring 2019 Purdue University

# ECE 255: L22

# MOS Current Mirrors and Basic Gain Cell

(Sedra and Smith, 7<sup>th</sup> Ed., Secs. 8.1-8.3)

Mark Lundstrom School of ECE Purdue University West Lafayette, IN USA

Lundstrom: 2019

- 1) HW7 due at 5:00 PM Friday, March 22

- 2) HW8 due at 5:00 PM Friday, March 29

- 3) Exam 3 is at 6:30 PM, Tuesday, April 2

- 4) Spice Project 2 will be due on April ?.

#### Google Official: on "ideal recruits"

"There is no single set of discrete skills one can learn that will last an entire career in high-tech," Johnson writes. Instead, "ideal recruits are creative, adaptable and autonomous, and they have achieved a deep understanding of core subjects such as math, physics and computer science that make it possible to have a razor-sharp intuition and an ability to assimilate new subjects and technologies quickly, without even the expectation of being trained; they train themselves on the skills du jour as the need arises and with minimum help or structure."

Bruce Johnson, the Atlanta site and engineering director for Google, in the Atlanta Journal-Constitution (12/23/11).

#### **Steven Chu on learning science:**

"Learning science is not about learning what a person did. You have to do that, but to really absorb it, you have to turn it around and cast it in a form **as if you invented it yourself**. You try to internalize it in such a way that it really becomes intuitive."

#### Muhammad Ali:

"I hated every minute of training, but I said, 'Don't quit. Suffer now and live the rest of your life as a champion."

-Muhammad Ali

http://www.brainyquote.com/quotes/quotes/m/muhammadal148629.html.

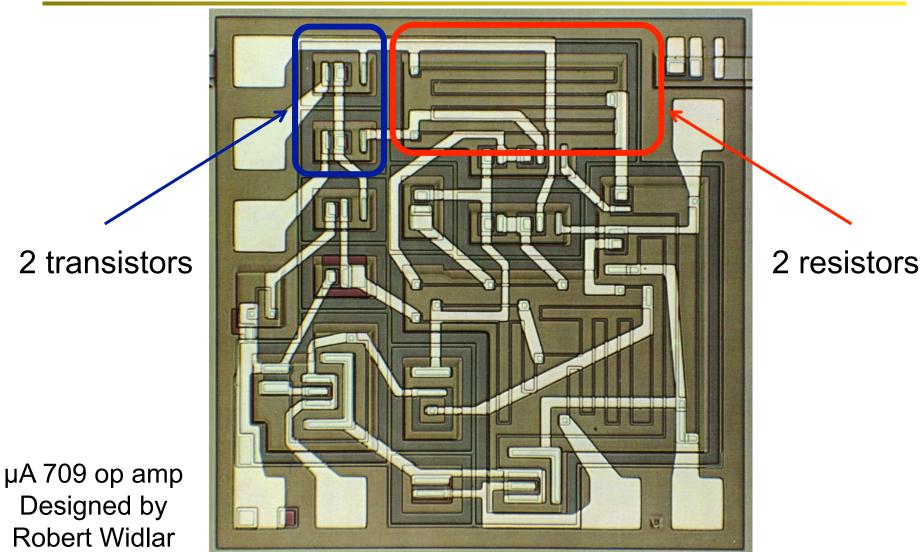

For the rest of the course, we will shift our focus to integrated circuit electronics.

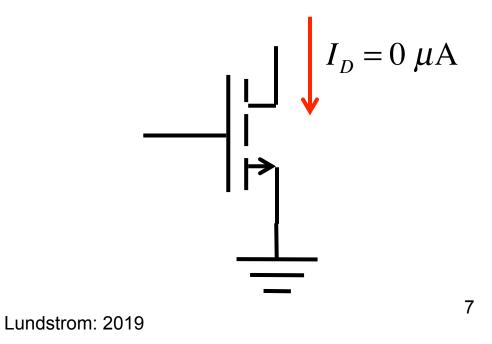

First question: How do we bias a MOSFET when it's on an a Si chip?

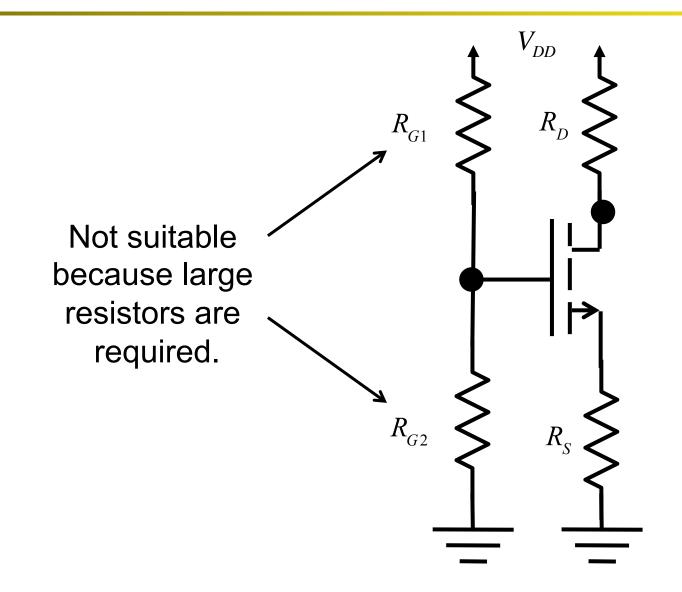

#### **Classic 4-resistor bias circuit**

### Why avoid large resistors?

http://www.computerhistory.org/revolution/digital-logic/12/281

- 1) Avoid large or moderate value resistors

- 2) Avoid large capacitors (but small ones, pF or less, are fine)

- 3) Use low voltage power supplies

- 4) Exploit the ability to "size" transistors (W/L for MOSFETs,  $A_E$  for bipolar)

- 5) Use CMOS unless bipolar is essential

# Outline

1) Introduction

#### 2) MOS Current Mirrors

3) CS Amplifiers with Active Loads

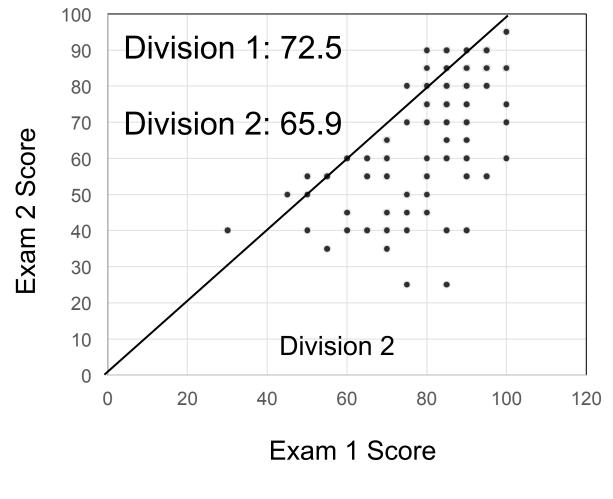

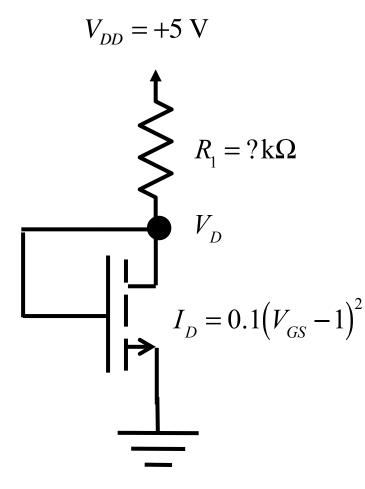

### **Review: MOSFET DC Design**

**Design for:**

$$I_D = 0.5 \text{ mA}$$

What region is this MOSFET operating in?

Is

$$V_{DS} \ge (V_{GS} - V_{tn})$$

$$V_{D} \ge \left(V_{D} - 1\right) \quad \checkmark$$

$$I_D = \frac{k'_n}{2} \frac{W}{L} \left( V_{GS} - V_{tn} \right)^2$$

Lundstrom: 2019

### Review: MOSFET DC Design

13

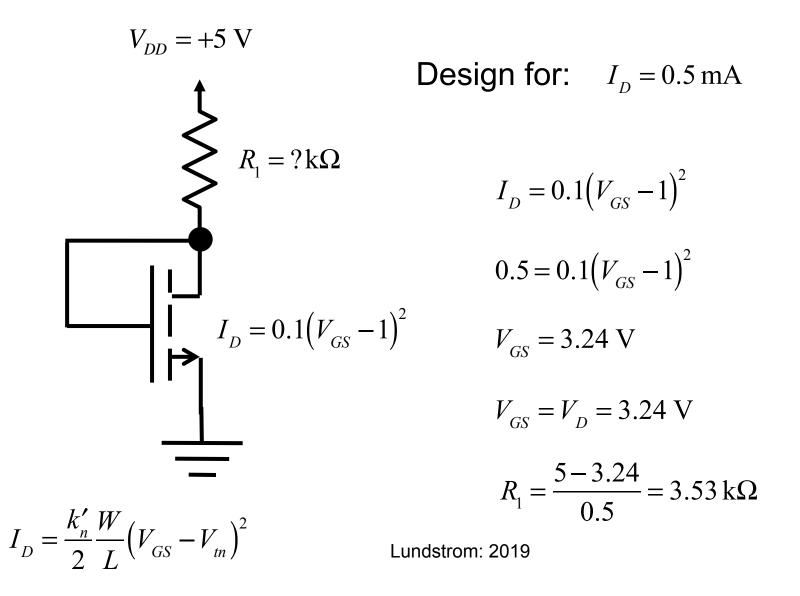

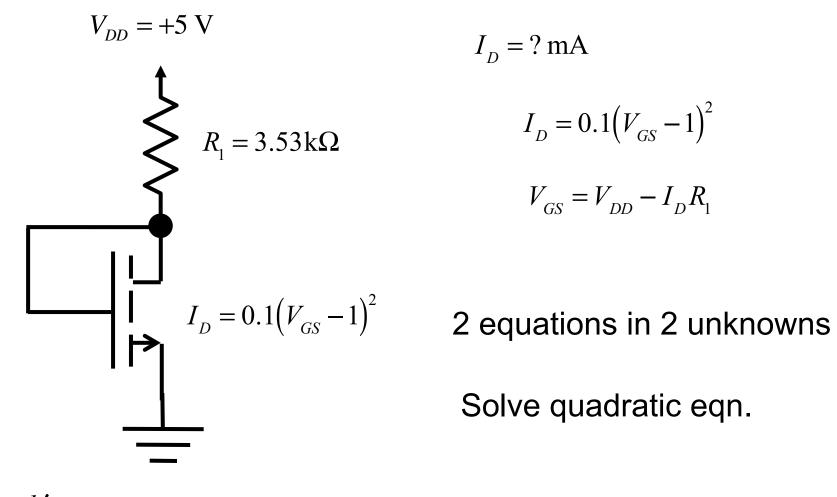

### Review: MOSFET DC Analysis

$$I_D = ? \text{ mA}$$

$$I_{D} = 0.1 (V_{GS} - 1)^{2}$$

$$V_{GS} = V_{DD} - I_D R_1$$

Solve quadratic eqn.

$I_D = \frac{k'_n}{2} \frac{W}{I} \left( V_{GS} - V_{tn} \right)^2$

Lundstrom: 2019

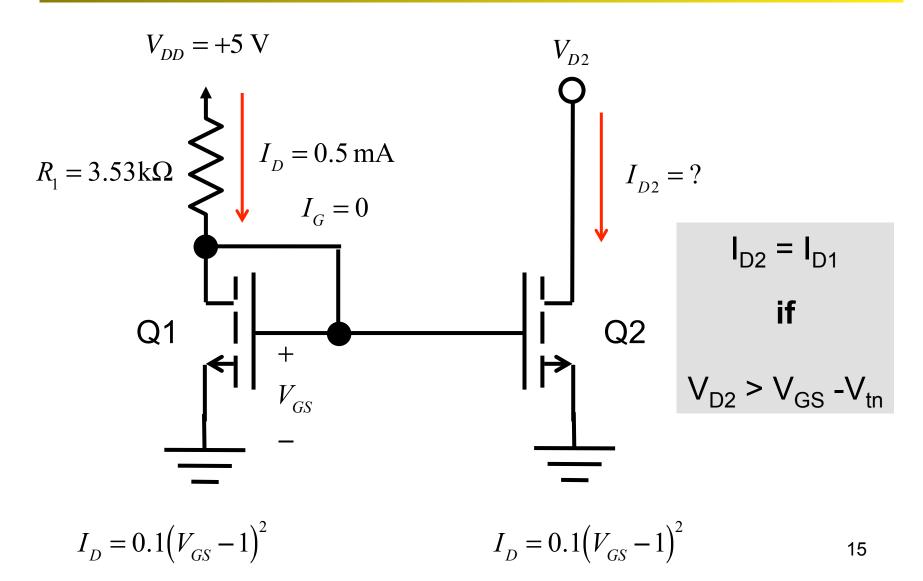

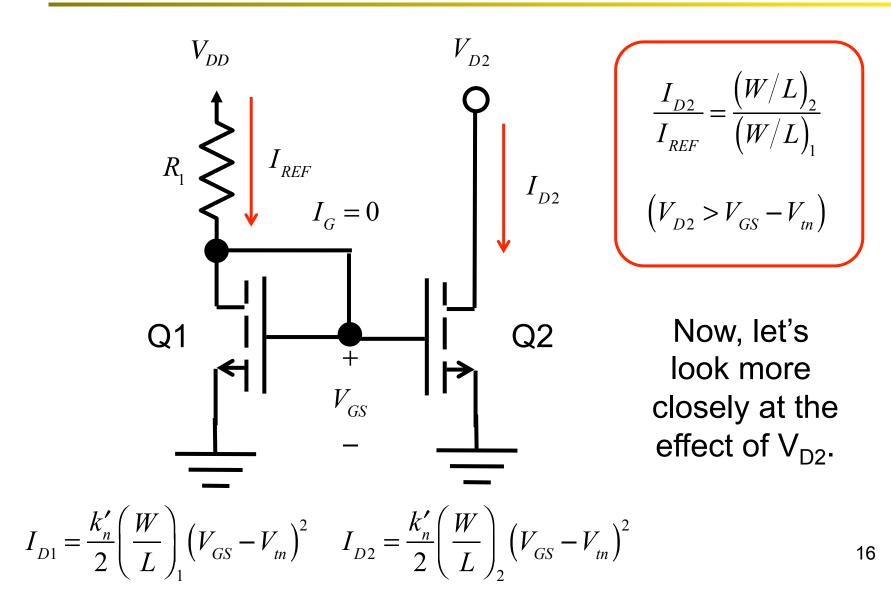

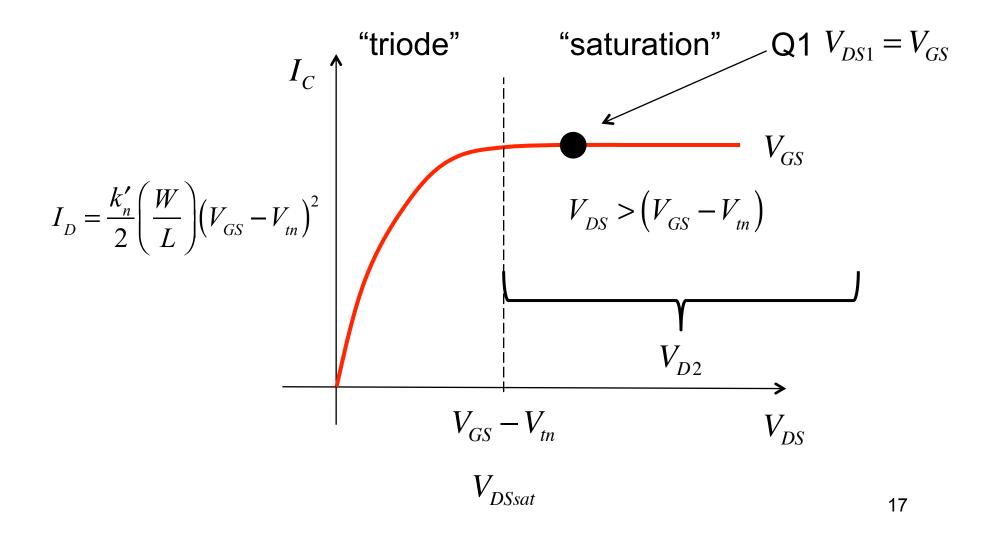

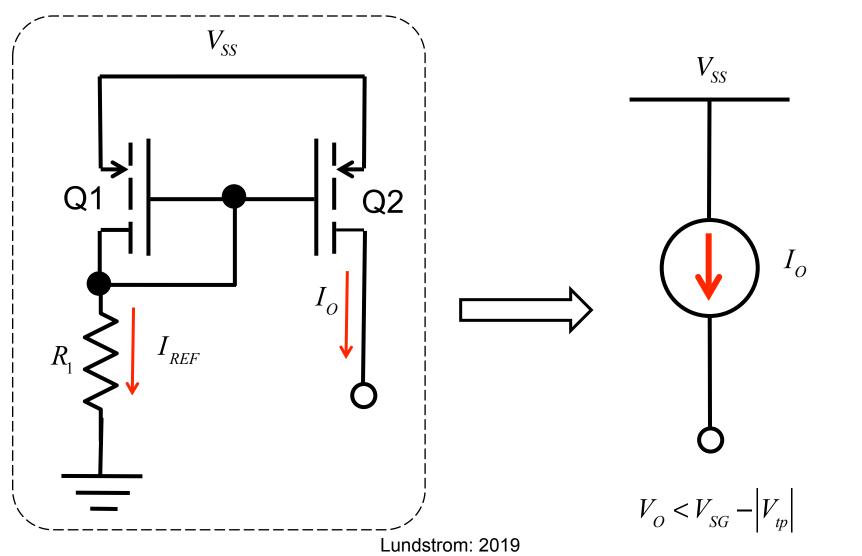

#### MOSFET "current mirror"

### MOSFET "current mirror"

#### **MOSFETs**

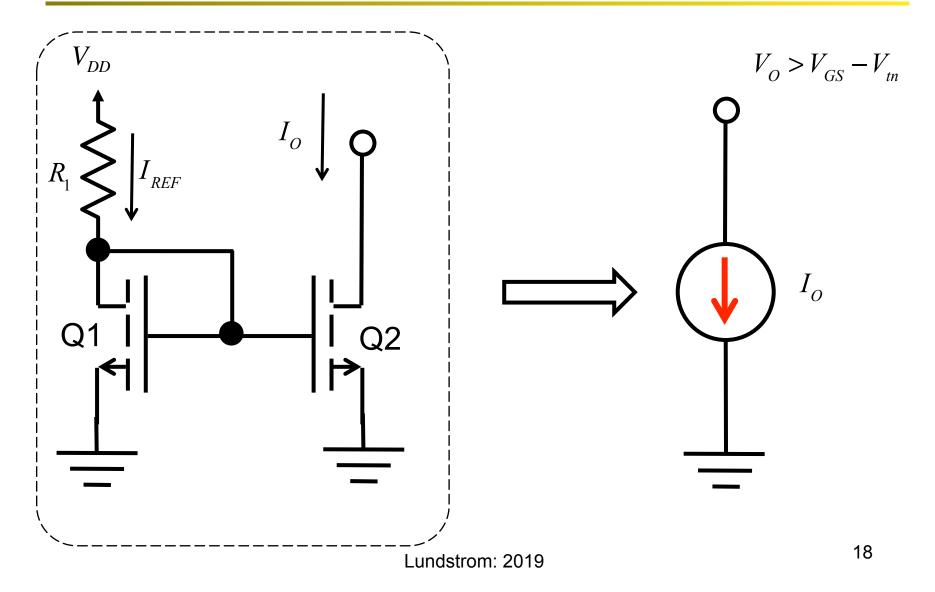

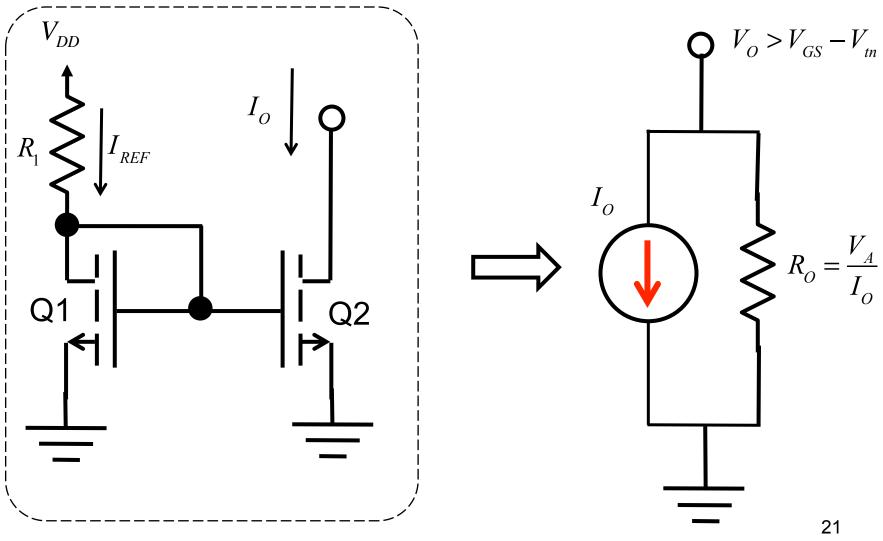

#### **MOSFET** current source

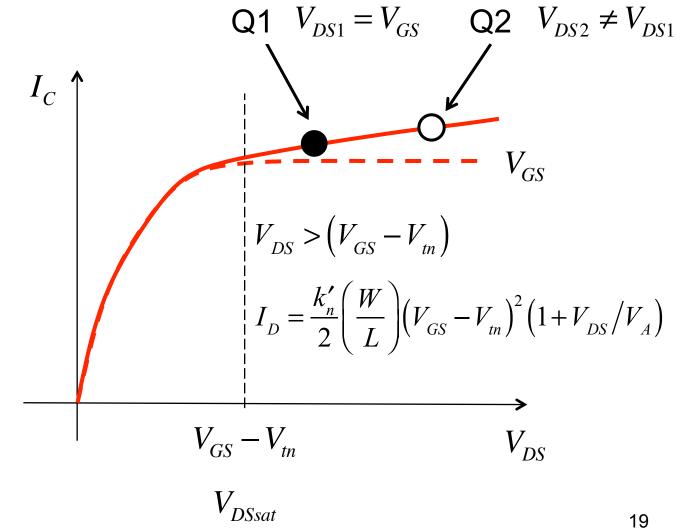

#### MOSFETs with output conductance

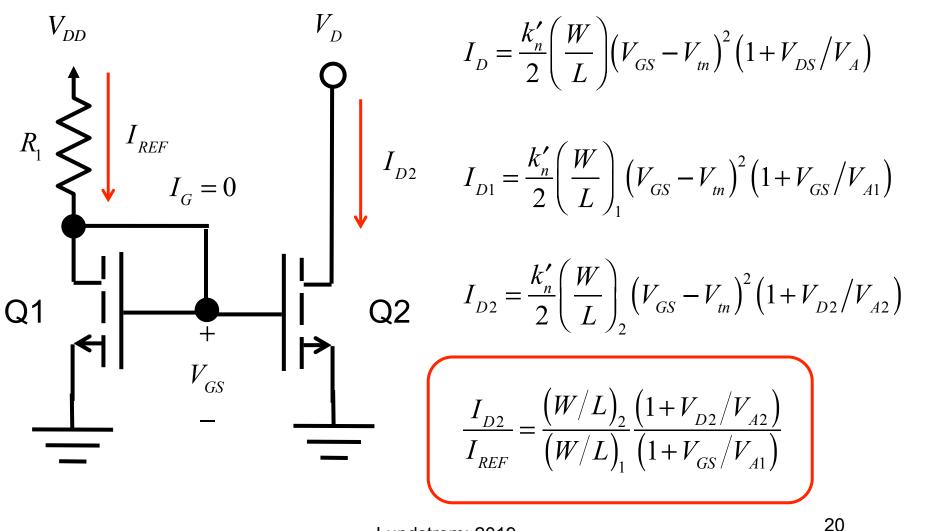

## Real MOSFET current mirror

Lundstrom: 2019

### RealMOSFET current source

Lundstrom: 2019

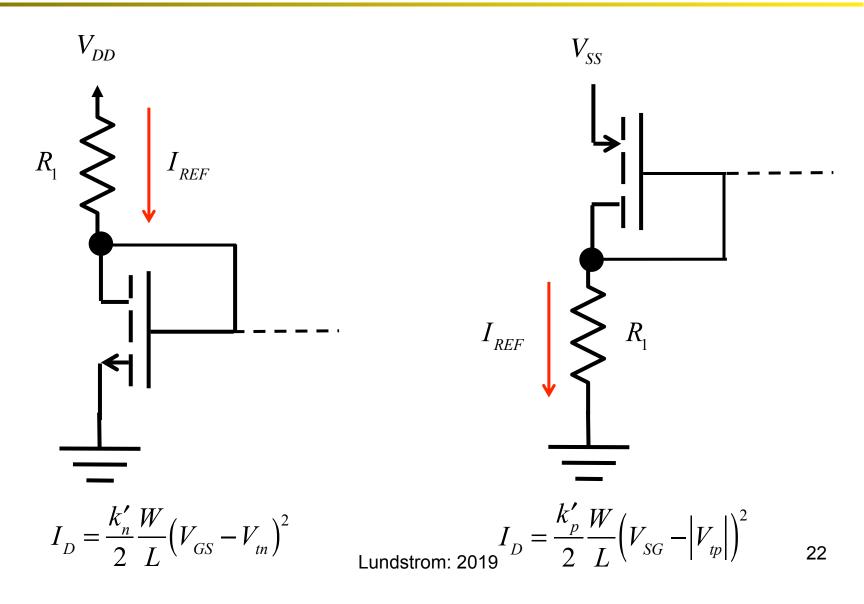

### NMOS vs. PMOS

### **PNP MOSFET current source**

23

Many sophisticated current mirror / current source circuits exist (e.g. to maximize output resistance).

See: Sedra and Smith 7<sup>th</sup> Ed. Sec. 8.6

# Outline

- 1) Introduction

- 2) MOS Current Mirror

- 3) CS Amplifiers with Active Loads

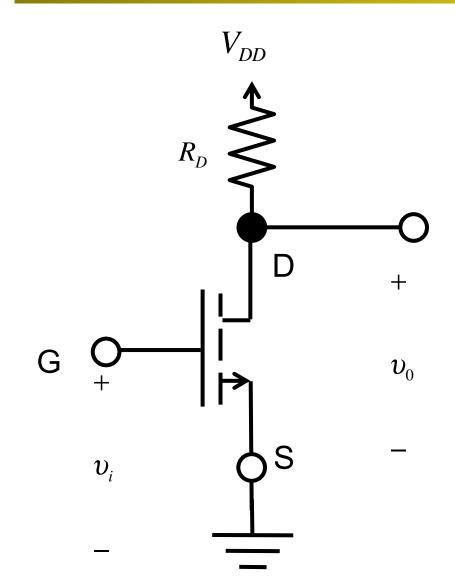

### **Common Source amplifier**

$$A_{v_o} = \frac{v_o}{v_i} = -g_m R_D$$

$$R_{in} = \infty$$

$$R_o = R_D$$

MOSFETs have modest  $g_m$ , so we need a very large drain resistor.

Two problems: ?

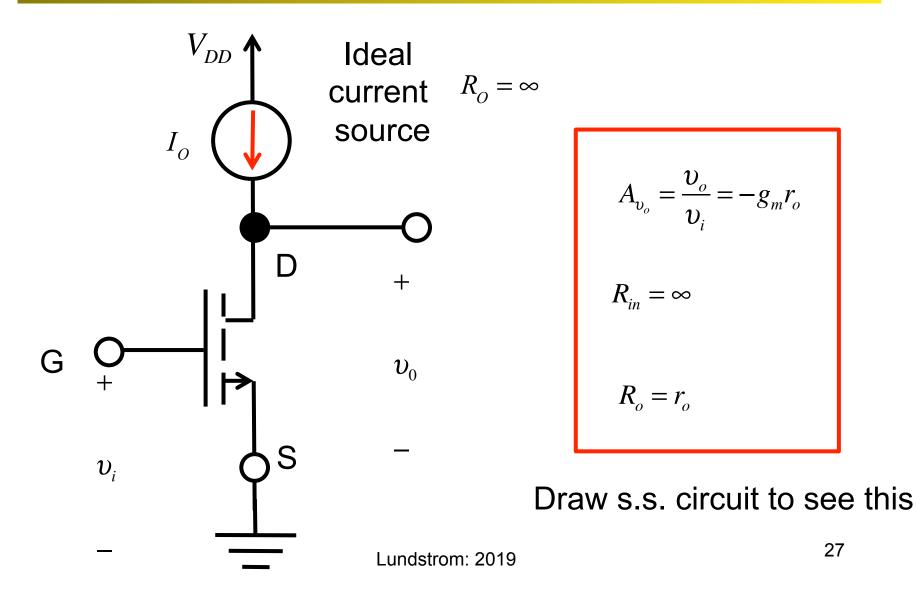

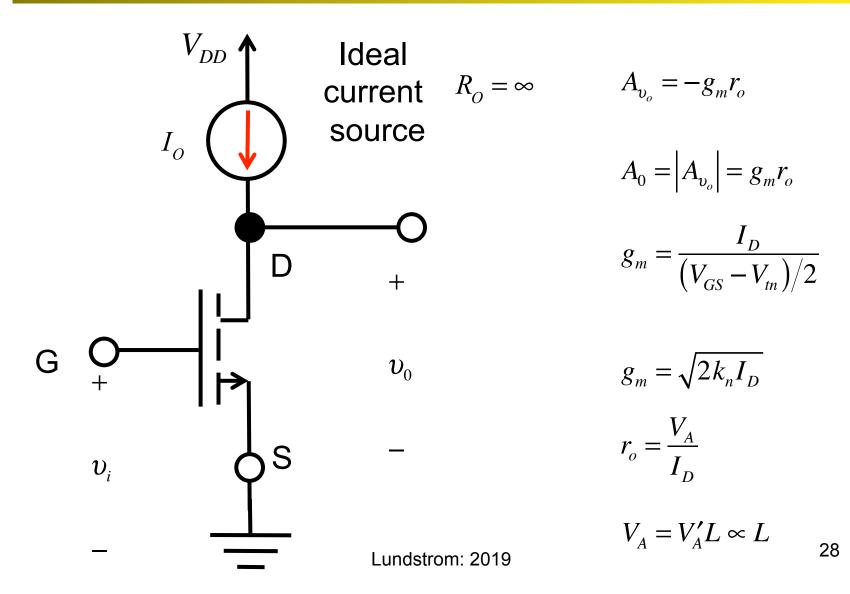

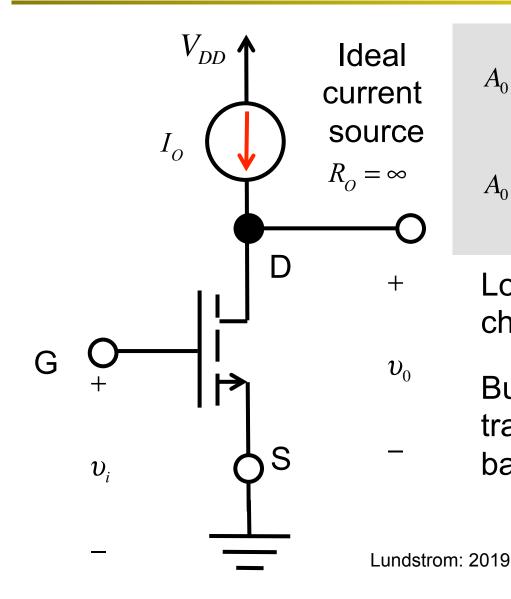

### Basic IC gain cell

Maximum gain ("intrinsic gain" / "self gain")

## Maximum (intrinsic/self) gain

$$A_{0} = \frac{V_{A}}{(V_{GS} - V_{tn})/2} = \frac{V_{A}'L}{(V_{GS} - V_{tn})/2}$$

$$A_{0} = \frac{V_{A}}{\sqrt{2k_{n}I_{D}}} = \frac{V_{A}'L}{\sqrt{2k_{n}I_{D}}}$$

Low currents and long channels give high gain

But, they give low transconductance and bandwidth

$$10 < A_0 < 40$$

29

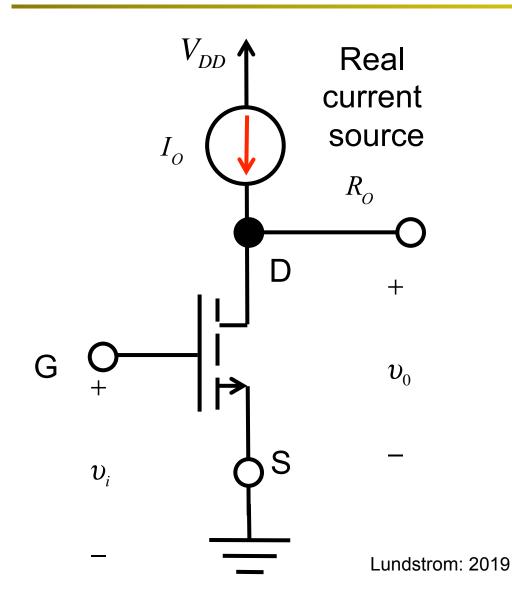

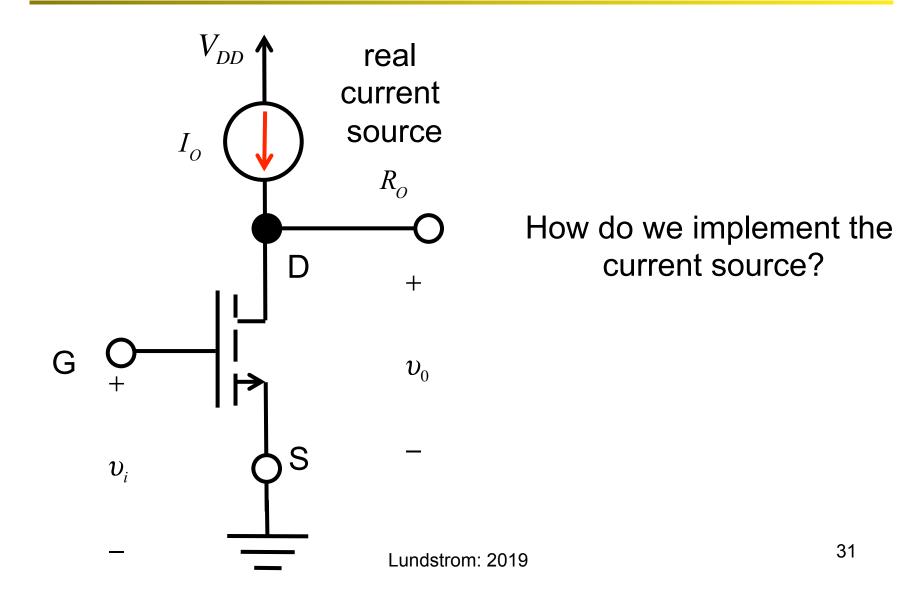

### Non-ideal current source

$$A_{v_o} = -g_m(r_o \parallel R_o)$$

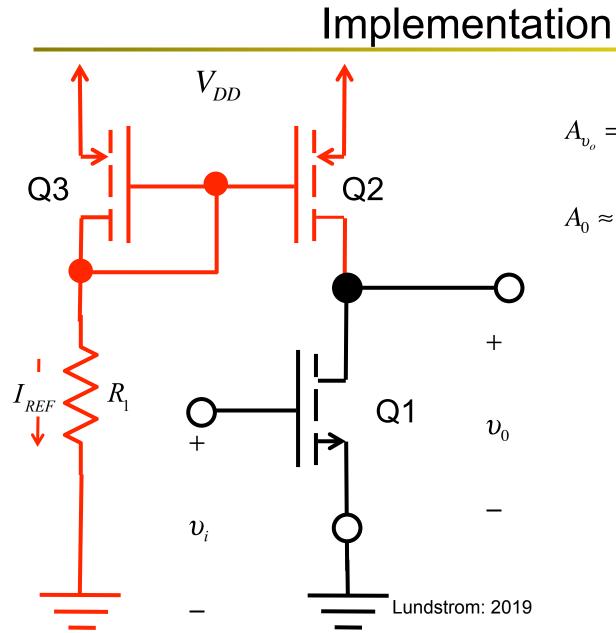

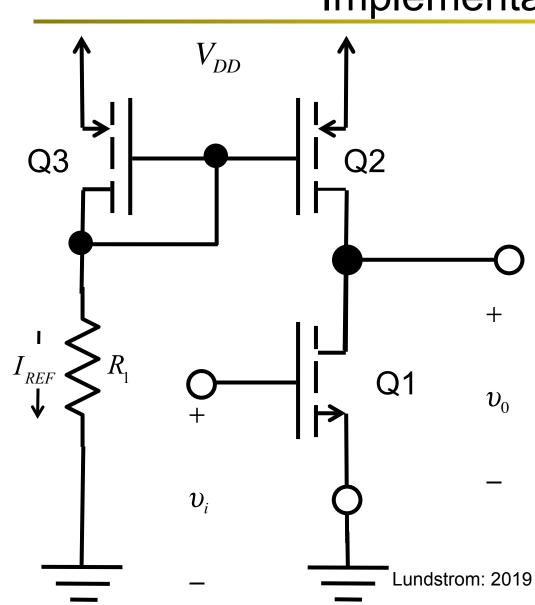

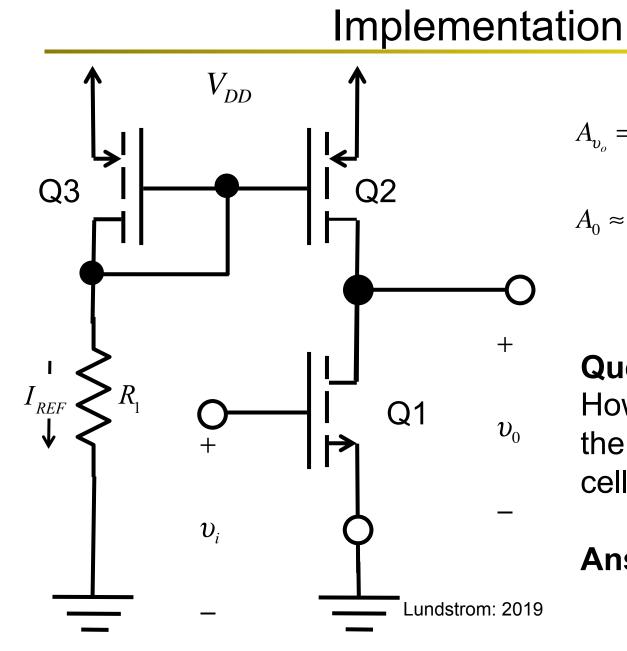

### Implementation

$$A_{v_o} = -g_m(r_{oN} \parallel r_{oP})$$

$$A_0 \approx \left(10 - 40\right) / 2$$

### Implementation

$$A_{v_o} = -g_m(r_{oN} \parallel r_{oP})$$

#### **Question:** How would we design this circuit for a gain of 5?

$$A_{v_o} = -g_m \left( r_{oN} \parallel r_{oP} \right)$$

$$A_0 \approx \left(10 - 40\right) / 2$$

#### **Question:**

How can we increase the gain of the basic cell?

Answer: Cascode

# Summary

Current mirrors are used extensively in analog IC design.

The basic common source amplifier suffers from low gain when implemented in Si. A solution must be found.

## Current Mirrors and Basic Gain Cell

- 1) Introduction

- 2) MOS Current Mirror

- 3) CS Amplifiers with Active Loads