## ECE-305: Spring 2018 MOS Field Effect Transistors (MOSFETs)

Pierret, Semiconductor Device Fundamentals (SDF) Chapters 15+16 (pp. 525-530, 563-599)

Professor Peter Bermel Electrical and Computer Engineering Purdue University, West Lafayette, IN USA pbermel@purdue.edu

# Outline

- 1. Review from Tuesday

- 2. Velocity saturation in simplified theory

- 3. Major Failure Modes

- A. Bulk charge theory for small transistors

- B. Bias Temperature Instability

- C. Short Channel Effects

- 4. Conclusion

#### **Approximations for Inversion Charge**

$$Q_{i} = -C_{o}(V_{G} - V_{T} - V) + qN_{A}(W_{T}(V) - W_{T}(V = 0))$$

$$= -C_o(V_G - V_T - V) + \sqrt{2qk_S\varepsilon_oN_A(2\phi_B + V)} - \sqrt{2qk_S\varepsilon_oN_A(2\phi_B)}$$

Approximations:

$$Q_i \approx -C_o(V_G - V_T - V)$$

Square law approximation ...

$Q_i \approx -C_o(V_G - V_T - mV)$  Simplified bulk charge approximation ...

4/5/2018

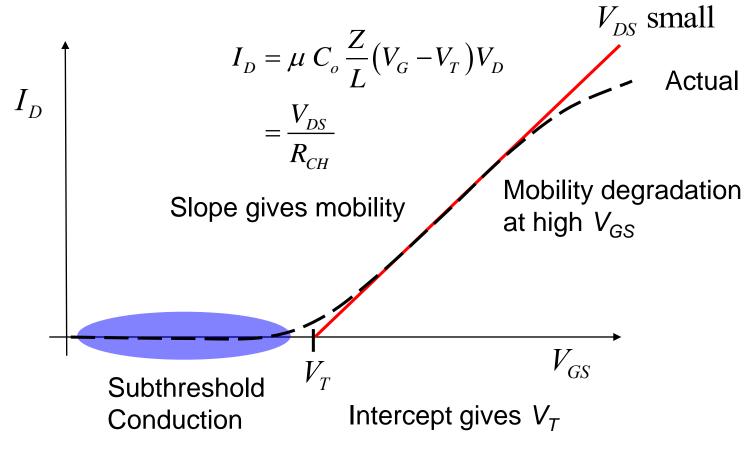

# Linear Region (Low $V_{DS}$ )

# Outline

- 1. Review from Tuesday

- 2. Velocity saturation in simplified theory

- 3. Major Failure Modes

- A. Bulk charge theory for small transistors

- B. Bias Temperature Instability

- C. Short Channel Effects

- 4. Conclusion

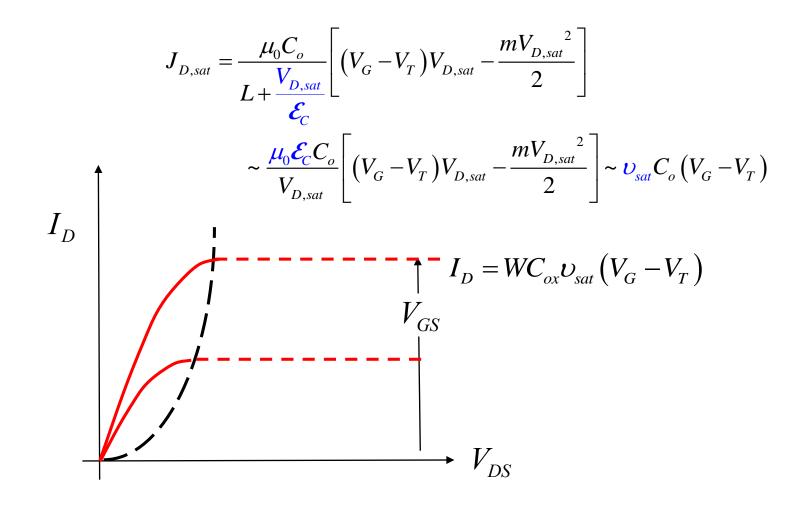

# Calculating $V_{\text{DSAT}}$

$$\upsilon_d = \frac{-\mu \mathcal{E}}{1 + (|\mathcal{E}|/\mathcal{E}_c)}$$

$$\frac{I_D}{Z} = \frac{\mu_o C_o}{L + \frac{V_D}{\mathcal{E}_c}} \left[ \left( V_G - V_T \right) V_D - m \frac{V_D^2}{2} \right]$$

Take log on both sides and then set the derivative to zero ....

$$V_{DSAT} = \frac{2(V_{G} - V_{T})/m}{1 + \sqrt{1 + 2\mu_{o}(V_{G} - V_{T})/m\nu_{sat}L}} < \frac{(V_{G} - V_{T})}{m}$$

4/5/2018

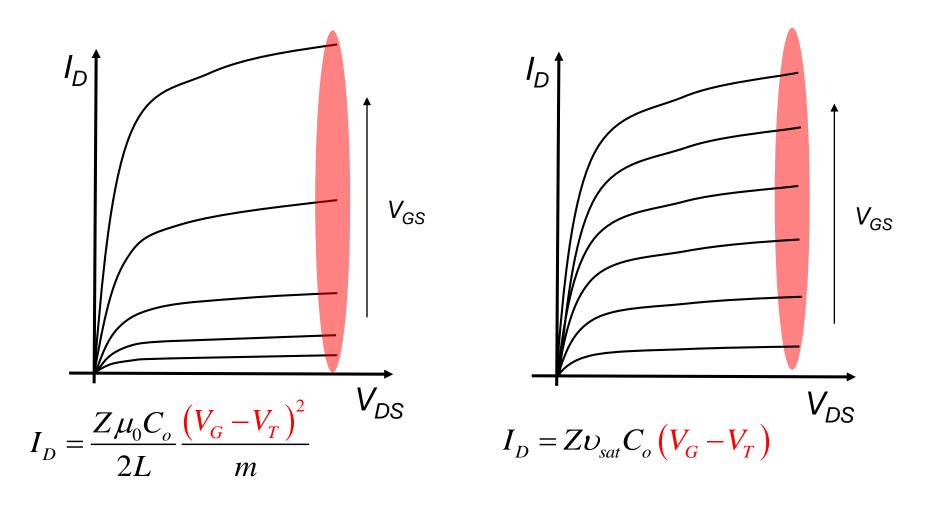

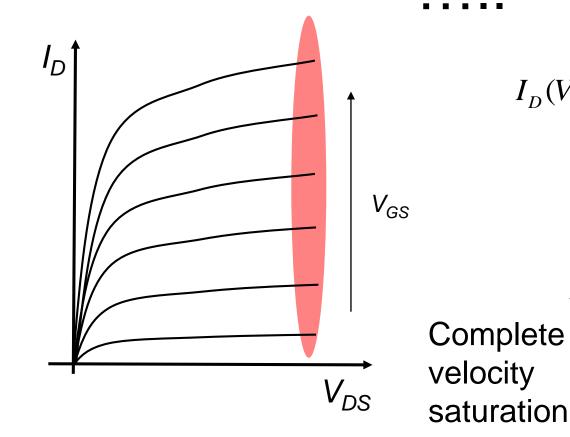

## **Velocity Saturation**

## 'Signature' of Velocity Saturation

4/5/2018

# $I_D$ and $(V_{GS} - V_T)$ : In practice

$$I_D(V_D = V_{DD}) \sim \left(V_G - V_T\right)^{\alpha}$$

#### **Topic: MOS-Capacitors**

Objective: Being comfortable in calculating the internal quantities of a MOScapacitor, including depletion width, surface electric field, oxide field, threshold voltage, etc.

Consider a silicon MOS-CAP with  $N_A = 10^{16} cm^{-3}$ . Calculate the maximum depletion width. Also, calculate the threshold voltage given the oxide thickness is 2 nm.

$$\phi_B = k_B T/q \ln(N_A/n_i) = 0.3473 \text{ V}, \text{ and } \psi_S = 2\phi_B = 0.6946V$$

$$x_D = \left[\frac{2 \kappa_s \epsilon_0 (\psi_s)}{q N_A}\right]^{0.5} = 0.3 \times 10^{-4} cm$$

$$V_t = \phi_s - \frac{Q_B}{C_o} = 0.6946 + \frac{1.6 \times 10^{-19} \times 10^{16} \times 0.3 \times 10^{-4}}{3.9 \times 8.85410^{-14} / (2 \times 10^{-7})} = 0.7225V$$

Explain to your satisfaction why: Capacitor area is absent, the dielectric constant is that of oxide, mobile charges are absent, and  $E_{ox} = -\frac{Q_B}{x_0}C_0$

10

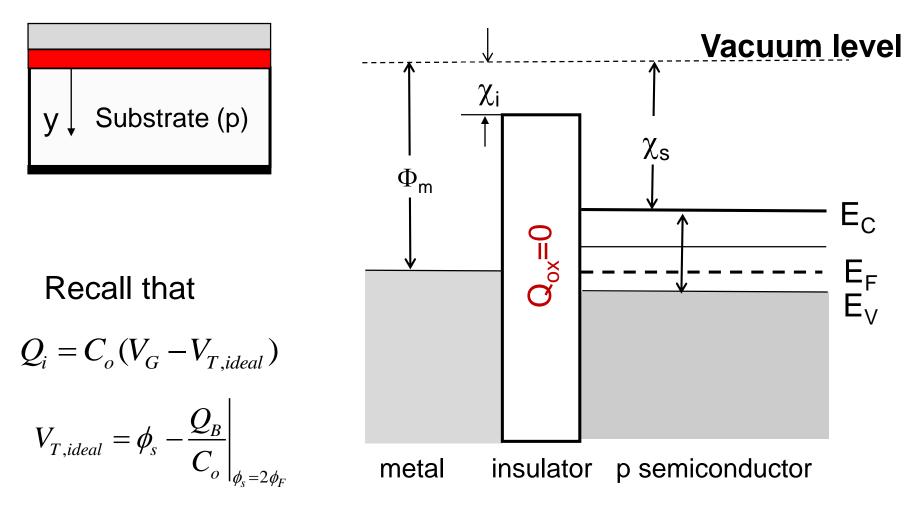

## **Topic: Nonideal MOS-Capacitors**

Objective: Given various nonideal quantities, such as workfunction difference, trapped charges, interface defects, calculate MOS-C electrical performance.

For an Al-Silicon MOS-C, with  $\Phi_M$ =4.10 eV and  $\chi_{Si}$  =4.05eV. If the doping is  $N_A = 10^{15} \ cm^{-3}$ , then calculate the flat band voltage.

$$\phi_B = k_B T/q \ln(N_A/n_i) = 0.29 \text{ V},$$

$$\phi_{ms} = \left(\chi_{Si} + \frac{E_G}{2} + \phi_B\right) - \Phi_M = 0.89V$$

Therefore, one must apply -0.89V to make the band flat.

Explain to your satisfaction why:

- (a) In the  $\phi_{ms}$  expression, if I wished to use  $E_G$  (not  $E_G/2$ ), how should I have modified the expression to get the same result.

- (b) Flatband voltage is negative, but the  $\phi_{ms}$  is positive?

- (c) Flatband voltage looks similar to the built-in voltage.

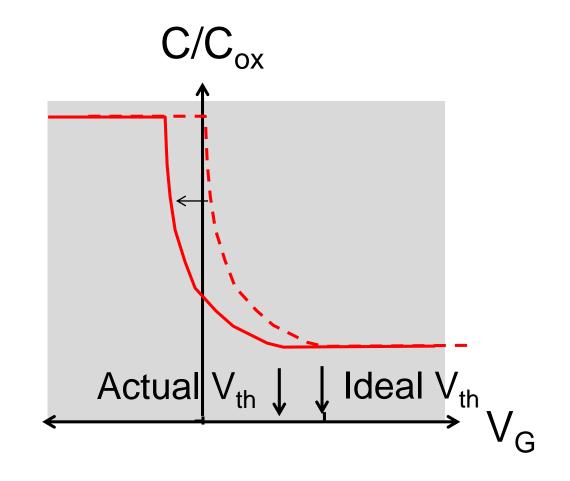

## **Topic: Nonideal MOS-Capacitors**

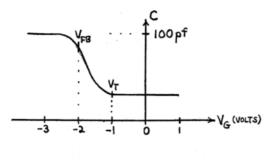

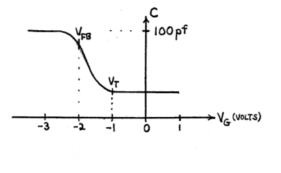

Objective: Learning to interpret an experimental C-V characteristics

Based on the C-V characteristics, answer the following questions

1. Is this a MOSCAP or MOSFET ? Ans. MOSCAP. Only a MOS-CAP shows such High-frequency inversion capacitance behavior.

2. What is the threshold voltage? Ans. -1V.

3. What is the flatband voltage? Ans. -2V

4. Is this a p-doped or n-doped semiconductor?

Ans. Accumulation occurs at negative voltage. Here, negative charge in the gate brings further increases the positive charge; hence, the substrate is p-type.

## **Topic: Nonideal MOS-Capacitors**

Objective: Learning to interpret an experimental C-V characteristics

Based on the C-V characteristics, answer the following questions

5. If the material becomes a channel of a MOSFET, will this be NFET or PFET? Ans. An N-MOSFET. MOSFET type is defined by the minority carriers (inversion)

6. Which voltage range would you use to determine the doping? Ans. -2V to -1V.

7. Which region will you check to determine the oxide thickness? Ans. Less than -2V.

8. Is this a small signal or a deep-depletion characteristics? Ans. Small signal because capacitance at  $V > V_T$  is a constant. Deep depletion would show linear reduction in capacitance with voltage.

4/5/2018

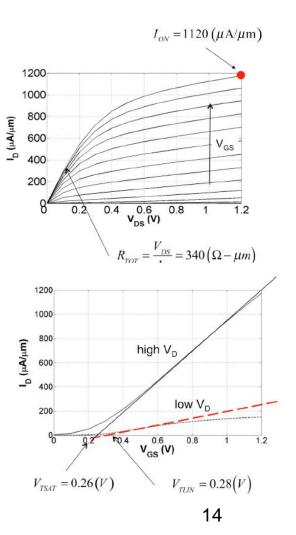

### Topic: MOSFET

#### Objective: Calculate electrical parameters based on experimental data

Relative dielectric constant:  $\kappa_{ar} = 4$

Series resistances:  $R_s = R_p = 100 \Omega - \mu m$

T = 300 KOxide thickness:  $x_0 = 2.2 \text{ nm}$ Power supply voltage:  $V_{DD} = 1.2 \text{ V}$ Actual channel length = 85 nm

Actual channel length = 85 nm From the so-called "on-current",  $I_D (V_{SD} = V_{DD}, V_{DS} = V_{DD})$ , estimate the average

velocity of electrons in the channel at the source end of the channel.

#### Solution:

$$\begin{split} \left\langle \upsilon(0) \right\rangle &= \frac{I_{ON}}{WQ_n(0)} \\ \mathcal{Q}_n(0) &= C_{ox} \left( V_{GS} - I_D R_S - V_T \right) \\ C_{ox} &= \frac{\mathcal{E}_{ox}}{x_o} = 1.6 \times 10^{-6} \text{ F/cm}^2 \\ \mathcal{Q}_n(0) &= \left( 1.6 \times 10^{-6} \right) \left( 1.2 - 1120 \times 10^{-6} \times 100 - 0.26 \right) = 1.32 \times 10^{-6} \\ \mathcal{Q}_n(0) / q &\simeq 8.3 \times 10^{12} \text{ cm}^{-2} \end{split}$$

$$\langle v(0) \rangle = \frac{I_{ON}}{WQ_n(0)} = \frac{1120 \times 10^{-6}}{10^{-4} \times 1.32 \times 10^{-6}} = 8.5 \times 10^7 \text{ cm/s}$$

$\langle v(0) \rangle = 8.5 \times 10^7 \text{ cm/s}$

Explain: Is this a long channel or a short channel transistor?

# Outline

- 1. Review from Tuesday

- 2. Velocity saturation in simplified theory

- 3. Major Failure Modes

- A. Bulk charge theory for small transistors

- B. Bias Temperature Instability

- C. Short Channel Effects

- 4. Conclusion

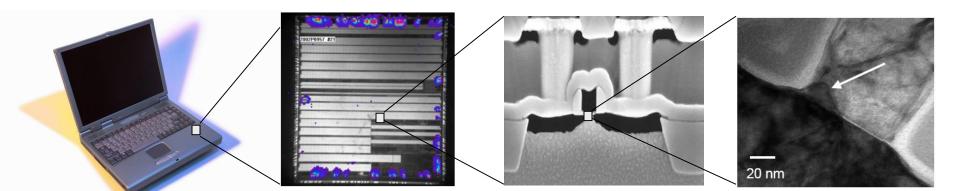

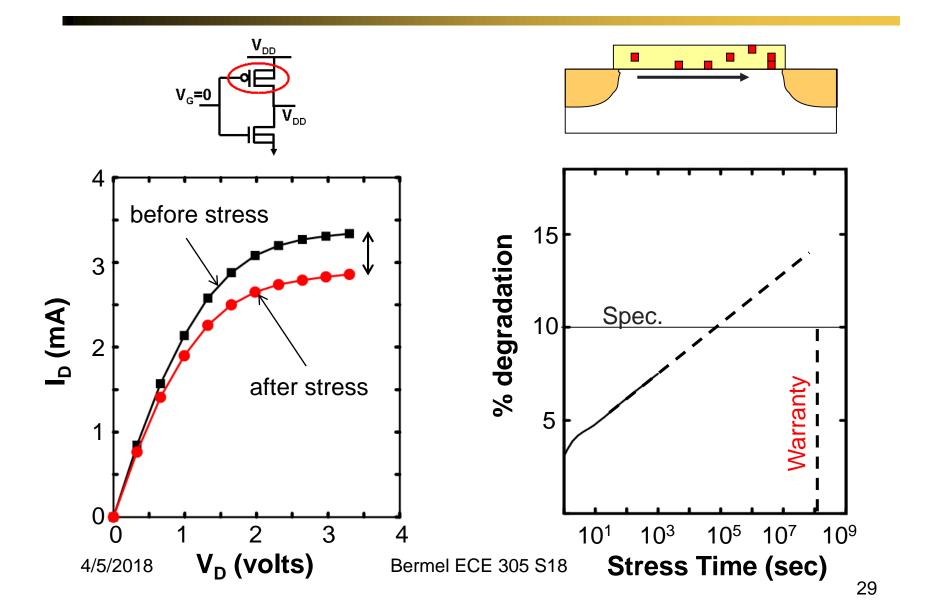

#### Warranty, product recall and other facts of life

In this course, you are learning to analyze/design MOSFETs that go in an IC ... ... because the ICs operate in incredibly harsh conditions, turning on and off trillions of time during its lifetime ....

... therefore the properties of the MOSFET keep changing. Eventually, S/D can be shorted, the gate oxide can break, etc ....

#### Measure of Flat-band shift from C-V Characteristics

## Idealized MOS Capacitor

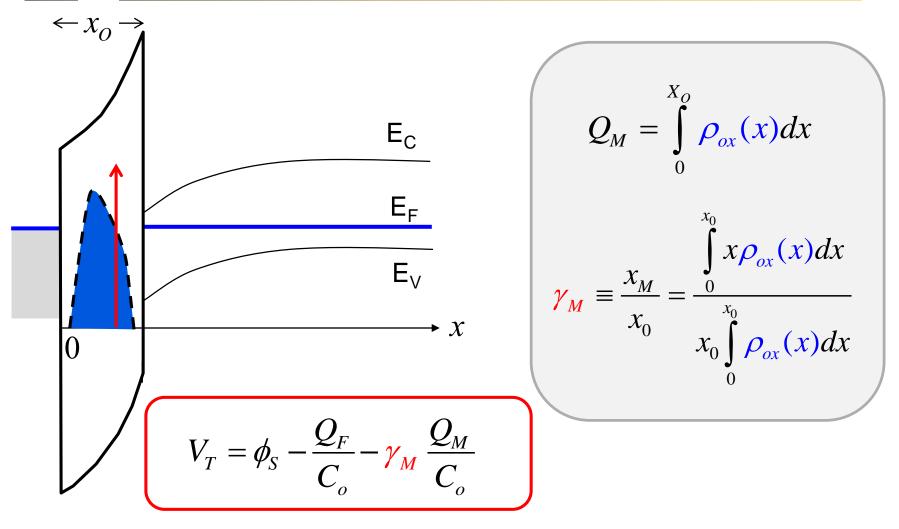

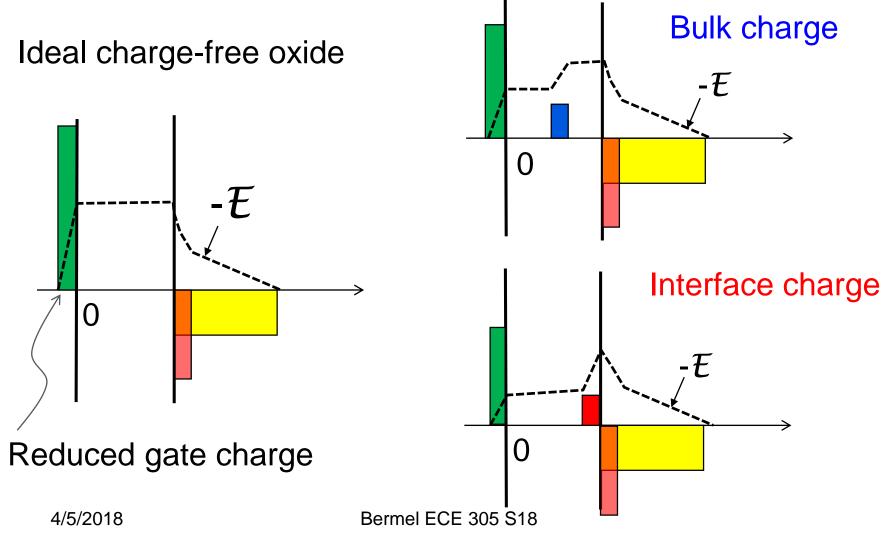

#### Distributed Trapped charge in the Oxide

## An Intuitive View

## Gate Voltage and Oxide Charge

$$V_G = \Delta V_{ox} + \phi_s$$

$$-\frac{dV_{ox}}{dx} = \mathcal{E}_{ox}(x) = \mathcal{E}_{ox}(x_0) - \int_{x}^{x_0} \frac{\rho_{ox}(x')dx'}{K_o \varepsilon_0}$$

$$\Delta V_{ox} = \frac{K_s}{K_o} x_0 \mathcal{E}_s(x_0) - \int_{0}^{x_0} dx \int_{x}^{x_0} \frac{\rho_{ox}(x')dx'}{K_o \varepsilon_0}$$

$=\frac{K_{S}}{K_{o}}x_{0}\mathcal{E}_{S}(x_{0})-\int_{0}^{x_{0}}\frac{x\rho_{ox}(x)dx}{K_{o}\varepsilon_{0}}$

4/5/2018

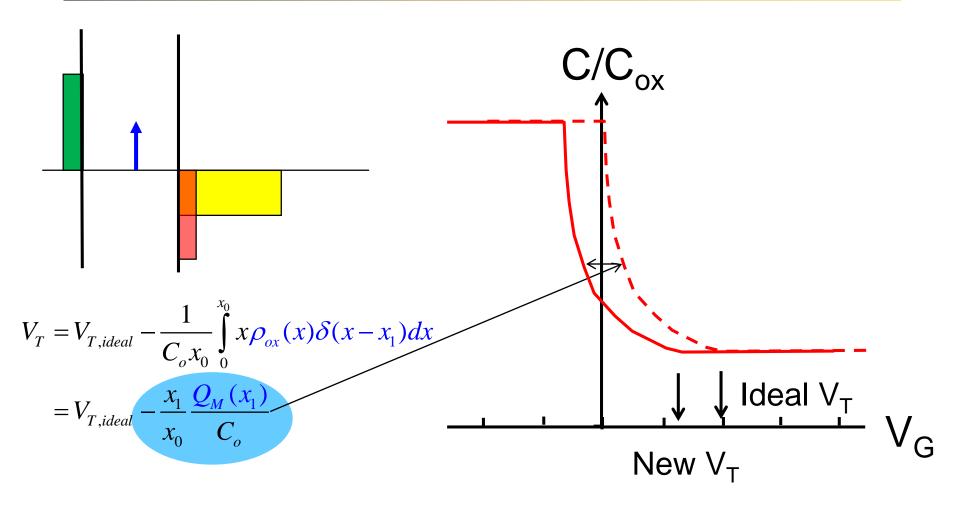

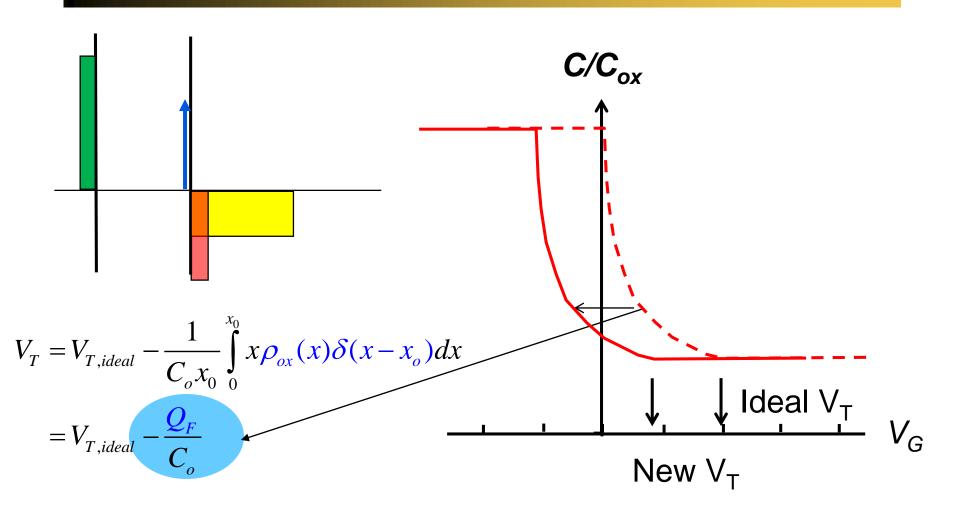

## Gate Voltage and Oxide Charge

$$\Delta V_{ox} = \frac{K_S}{K_o} x_0 \mathcal{E}_S(x_0) - \int_0^{x_0} \frac{x \rho_{ox}(x) dx}{\left(\frac{K_o \mathcal{E}_0}{x_0}\right) x_0} = V_{T,ideal} - \frac{1}{C_o x_0} \int_0^{x_0} x \rho_{ox}(x) dx$$

$$= \frac{K_S}{K_o} x_0 \mathcal{E}_S(x_0) - \frac{1}{C_o x_0} \int_0^{x_0} x \rho_{ox}(x) dx = V_{T,ideal} - \frac{Q_M}{C_o} \gamma_M$$

$$V_{th} = \Psi_{s}(= 2\phi_{F}) + \Delta V_{ox}$$

=  $(\Psi_{s}(= 2\phi_{F}) + \frac{\kappa_{S}}{\kappa_{ox}} x_{0} \mathcal{E}_{S}(x_{0})) - \frac{1}{C_{o} x_{0}} \int_{0}^{x_{0}} x \rho_{ox}(x) dx$

4/5/2018

## Interpretation for Bulk Charge

## Interpretation for Interface Charge

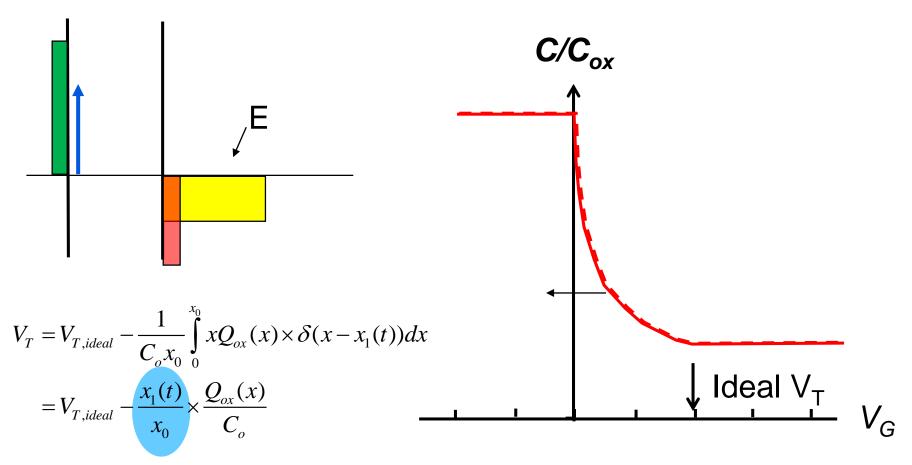

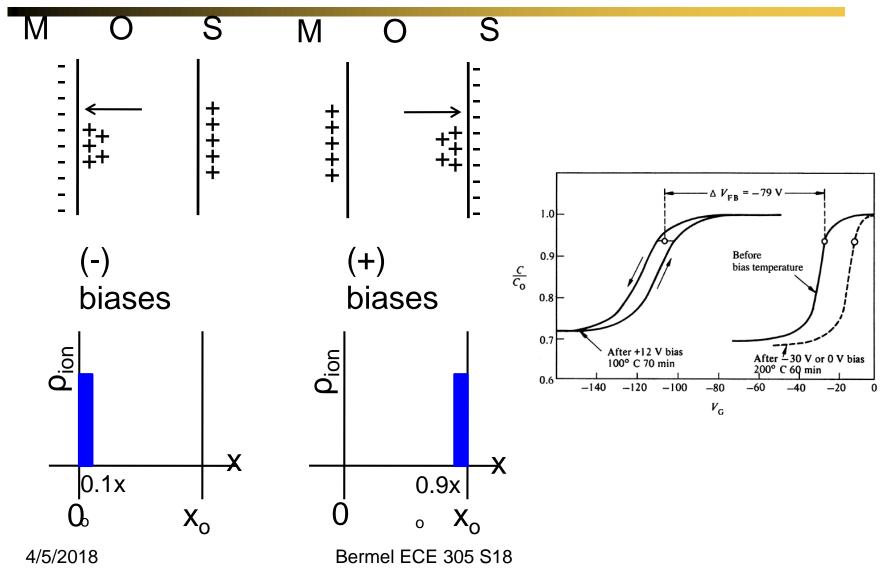

#### **Time-dependent shift of Trapped Charge**

Sodium related bias temperature instability (BTI) issue

4/5/2018

Bermel ECE 305 S18

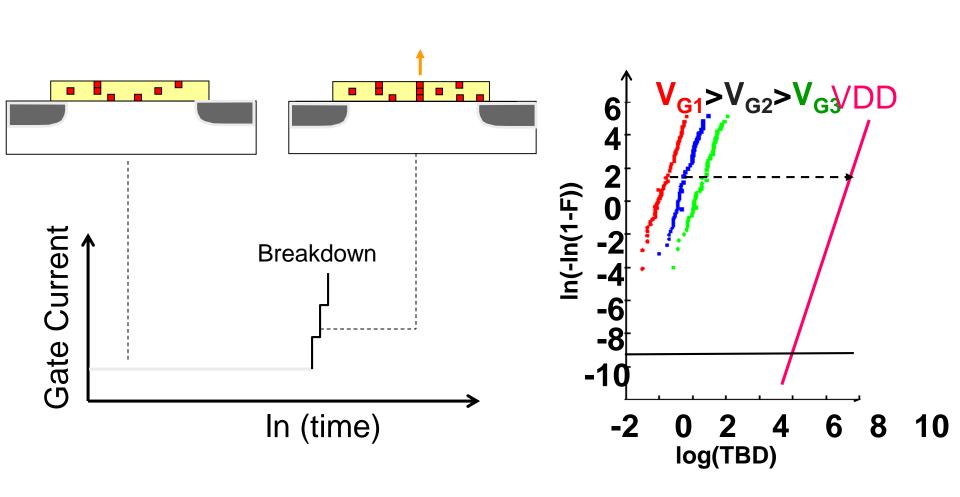

#### **Dielectric Breakdown**

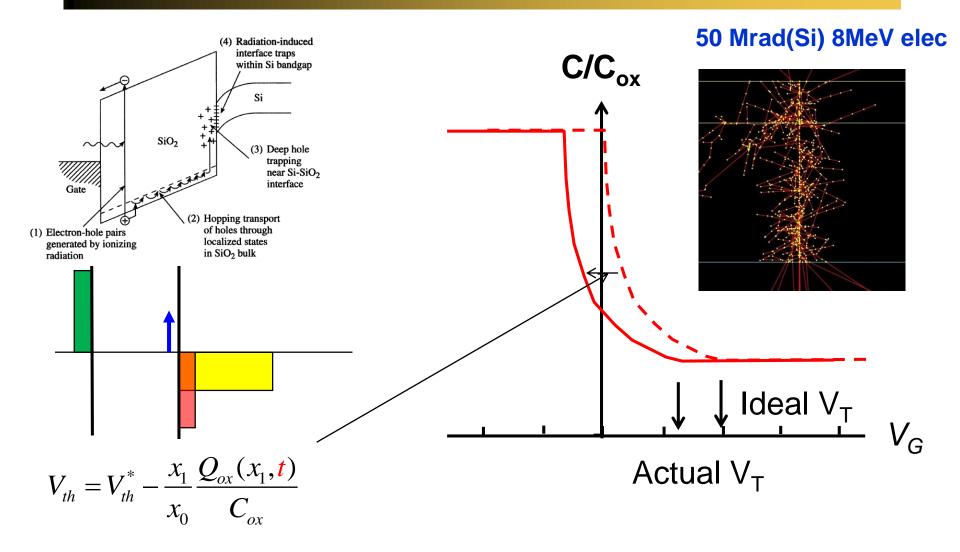

## **Radiation Induced Charge Buildup**

#### Bias Temperature Instability (Experiment)

#### **Negative Bias Temperature Instability**

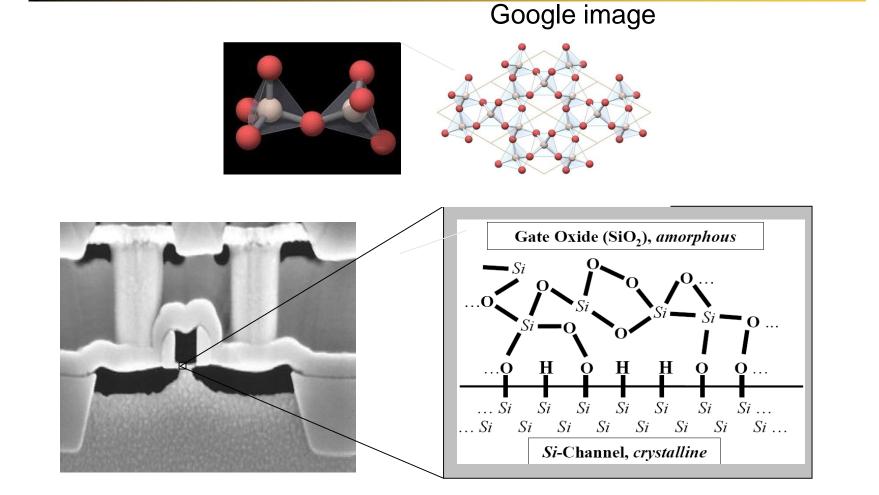

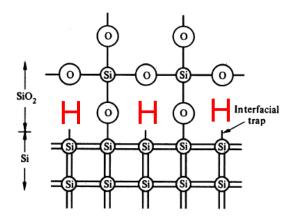

## SiO and SiH Bonds

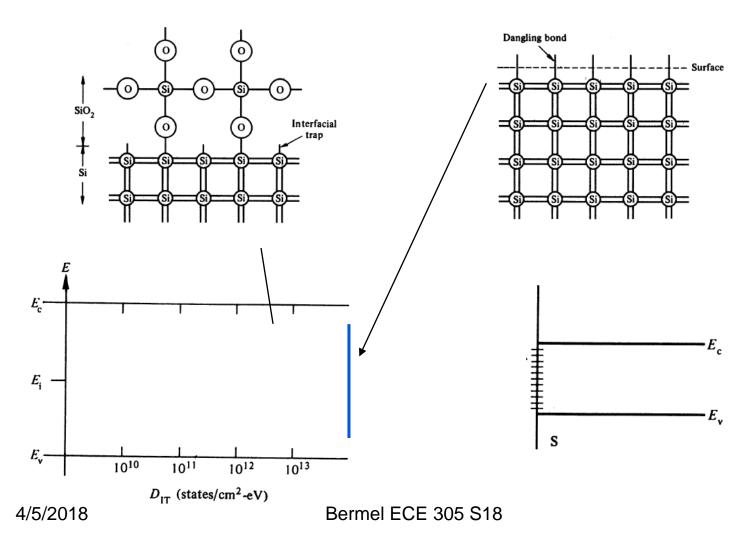

## **Interface States**

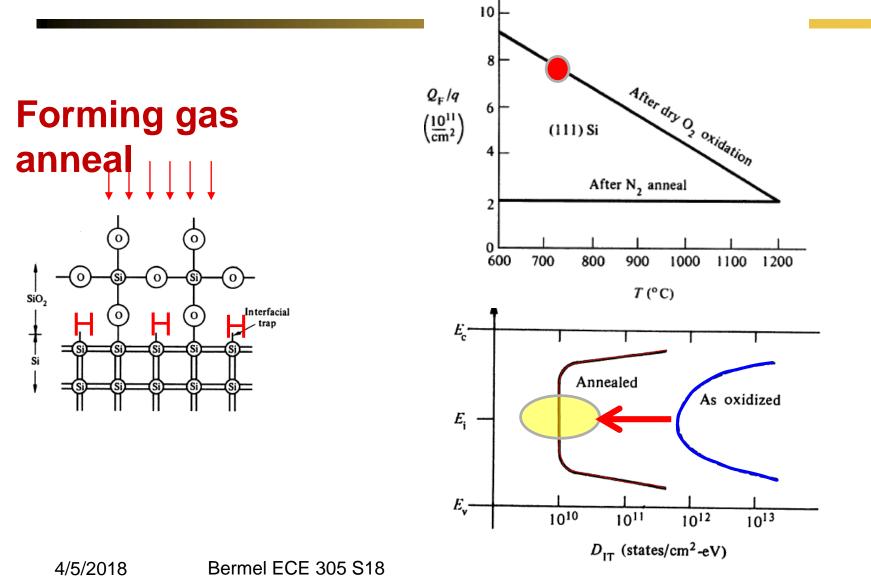

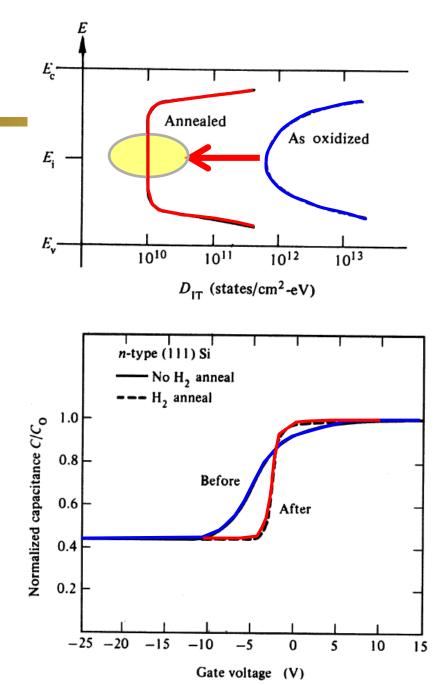

## 'Annealing' of Interface States

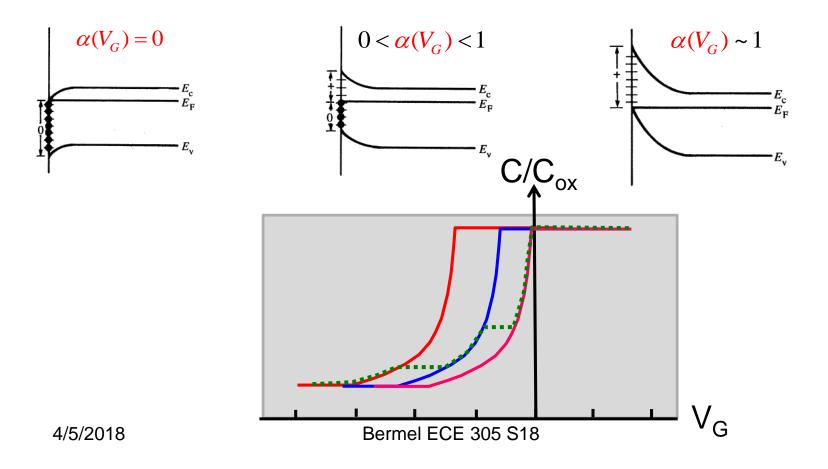

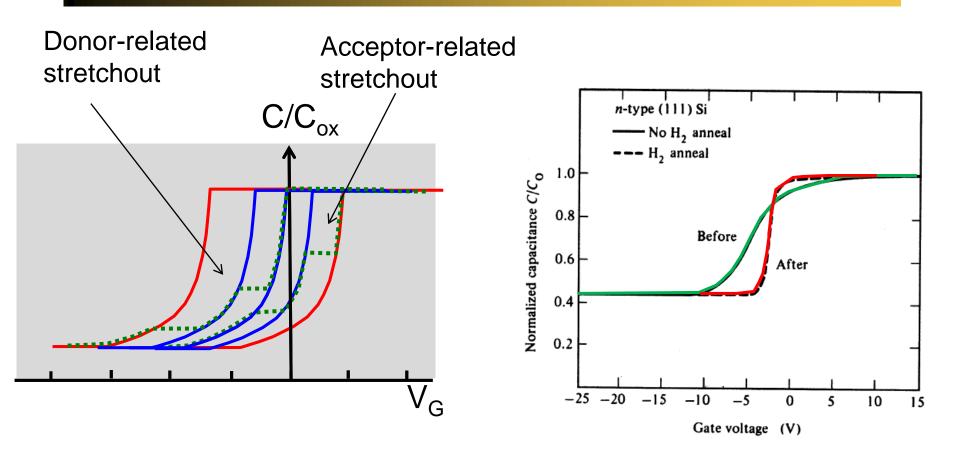

## **C-V Stretch Out**

#### Forming gas anneal

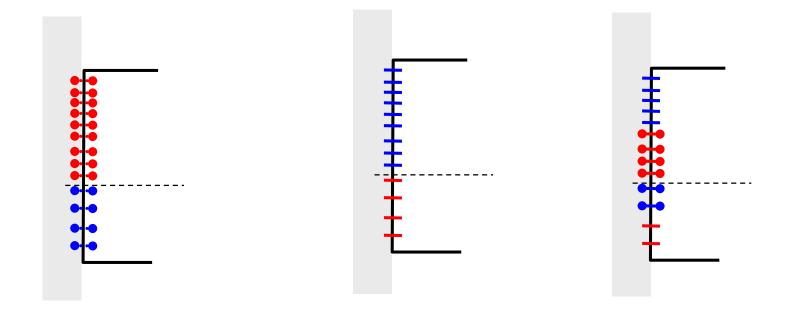

#### Nature of Donor and Acceptor Traps

Donor level Positive when empty Neutral when full

Acceptor level Combination when Neutral when empty both are present Negative when full

Bermel ECE 305 S18

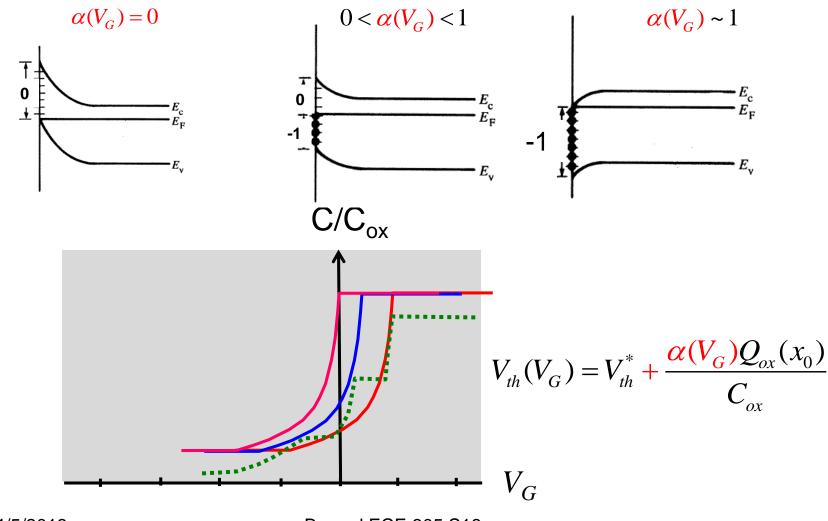

## **Donor-like Interface States**

$$V_{th} = V_{th}^* - \frac{1}{C_{ox} x_0} \int_0^{x_0} x \times \alpha(V_G) \times Q_{ox}(x) \delta(x - x_o) dx = V_{th}^* - \frac{\alpha(V_G) Q_{ox}(x_0)}{C_{ox}}$$

## **Acceptor-like Interface States**

Bermel ECE 305 S18

#### Acceptor and Donor Traps Combined

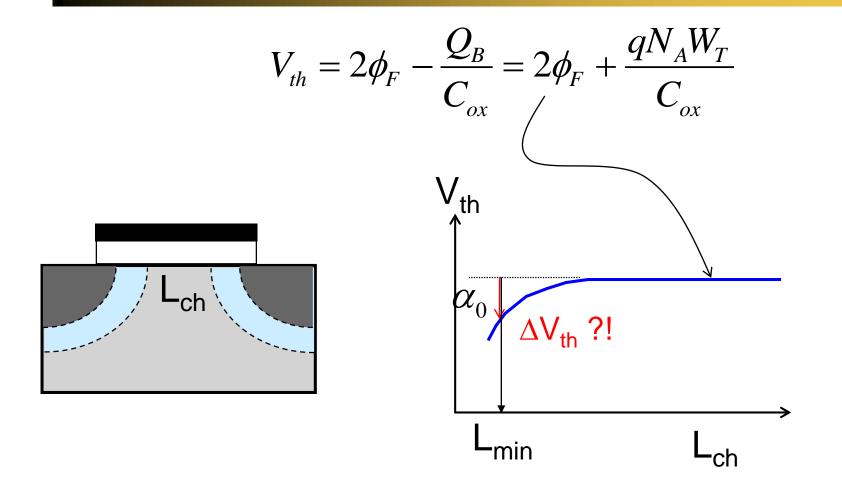

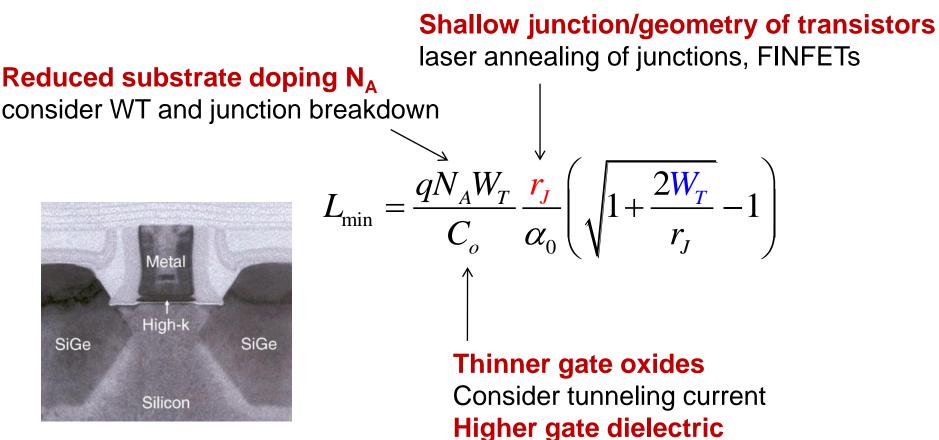

## Short Channel Effect: V<sub>th</sub> Roll-off

# How to reduce $V_{th}$ roll-off ...

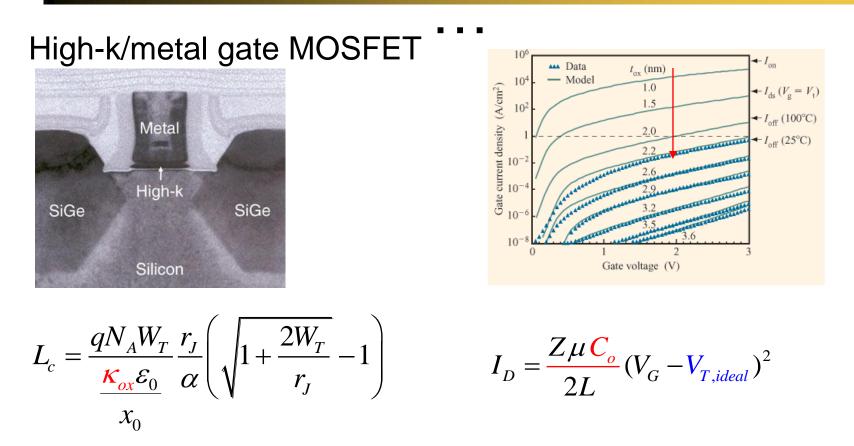

High-k/metal gate MOSFET

Consider bulk traps

# Advantages of High-k Dielectric

Thicker oxide  $(x_0)$  for same capacitance ...

... ensures the drive-current is not reduced , but tunneling current is suppressed.

4/5/2018

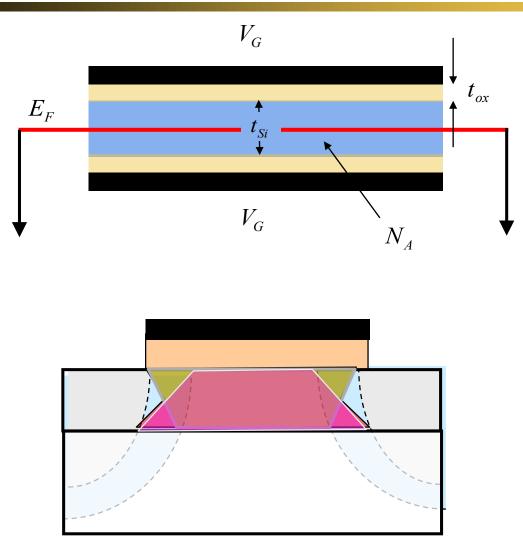

## Solution: Ultra-thin Body SOI

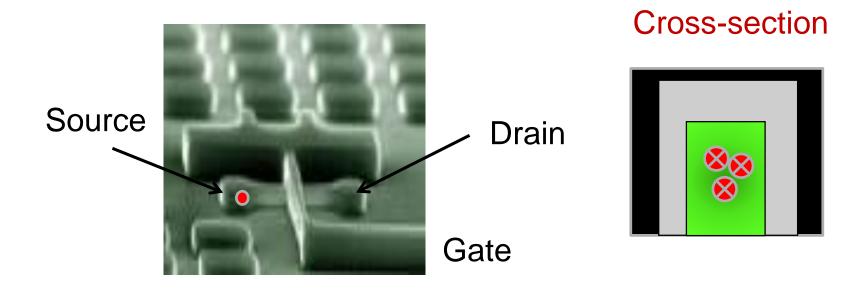

## Example: FINFET, OmegaFET, X-FET

# Outline

- 1. Review from Tuesday

- 2. Velocity saturation in simplified theory

- 3. Major Failure Modes

- A. Bulk charge theory for small transistors

- B. Bias Temperature Instability

- C. Short Channel Effects

- 4. Conclusion

## Conclusion

- 1) Ideal and non-ideal MOSFETs currents above threshold can be predicted using a simplified bulk-charge theory

- There are a variety of failure modes that can degrade performance over time: particularly dielectric breakdown and negative-bias temperature instability

- 3) Short channel effects are a serious concern for MOSFET scaling, and novel approaches have been proposed to solve them. Fortunately, electrons travel from source to drain without scattering in very short channel transistors. A considerably simpler theory applies here.