## Measurement of Seebeck coefficient perpendicular to SiGe superlattice

Yan Zhang<sup>1</sup>, Gehang Zeng<sup>2</sup>, Rajeev Singh <sup>1</sup>, James Christofferson <sup>1</sup>, Edward Croke <sup>3</sup>, John E. Bowers <sup>2</sup> and Ali Shakouri <sup>1</sup>,

#### Abstract

Seebeck coefficient is one of the key parameters to evaluate the performance of thermoelectric coolers. However, it is very difficult to directly measure Seebeck coefficient perpendicular to thin film devices because of the difficulty of creating a temperature gradient and measuring localized temperature and voltage change simultaneously. In this paper, a novel method is described and it is used to measure the Seebeck coefficient of SiGe superlattice perpendicular to the layers<sup>1</sup>. measurement was achieved by integrating a thin film metal wire as a temperature sensor and heat source on top of the SiGe superlattice coolers. Extensive micro thermoreflectance imaging characterization was performed to ensure uniform temperature distribution on top of the thin film device. Details of the experimental set-up and measurement technique are discussed. By analyzing the measured thermoelectric voltage for various device sizes and superlattice thickness, Seebeck coefficient of the superlattice material perpendicular to the layers is deduced.

#### Introduction

In VLSI circuits, high heating power density is one of the bottlenecks that limits the reliability and performance of the chip in high-speed, high-density applications. Conventional bulk Bi<sub>2</sub>Te<sub>3</sub> coolers have limited applications in microelectronic circuits due to low cooling power density and difficulty of integration and packaging<sup>3</sup>. Conventional Si or III-V based semiconductor materials have a low thermoelectric figure-of-merit and they are not suited for cooling application There have been several excellent recent studies on BiTe-based thin film coolers with high thermoelectric figure-of-merit<sup>2</sup>. We are concentrating on SiGebased coolers for the possibility of direct integration with silicon circuits. Use of thermionic emission in heterostructure superlattices can improve the figure-of-merit by selective emission of hot electrons above potential barriers and by reducing the phonon heat conduction in multiplayer materials. SiGe and SiGeC-based coolers have already demonstrated a cooling power density exceeding 500 W/cm<sup>2</sup> and a maximum cooling of 4<sup>0</sup>C at room temperature.

In this paper, we focus our study on the Seebeck coefficient perpendicular to SiGe superlattice layers. Although there are some papers on the cross-plan thermal conductivity, electrical conductivity of SiGe superlattice<sup>5,67,8</sup>. There are still very few papers on the experimental measurements of the Seebeck coefficient

perpendicular to the thin film because of its difficulty to measure the voltage and temperature change simultaneously. We used an integrated thin film resistor both as a heater and a sensor on top of the SiGe superlattice microcooler. The processing was done using the standard semiconductor fabrication process 11.

In a linear transport regime, the Seebeck coefficient is defined as the voltage produced across two points on a material divided by the temperature difference between

them. This has an expression of

$$S = \frac{\Delta V}{\Delta T}$$

12. Seebeck

coefficient is the main parameter to evaluate performance of thermocouples. It is also the key parameter to calculate the ZT, the thermoelectric figure of merit, which has the express ion of:

$$ZT = S^2T / rK_T$$

(Eqn.1)

Where S: Seebeck coefficient; T: temperature;  $\rho$ : electrical resistivity;  $K_T$ : Thermal conductivity<sup>12</sup>.

#### **Experiments**

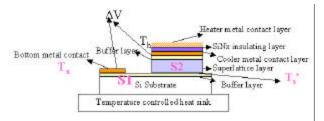

The micro-cooler structure is based on cross-plane electrical transport theory. The main part of the cooler is a superlattice structure of 80Å Si/40 Å Si<sub>0.7</sub>G e<sub>0.3</sub> grown at 500°C, doped with boron to about 5x10<sup>19</sup> cm<sup>-3</sup>. The buffer layer was grown on top of the silicon with the structure of 1 um  $SiGe_{0.1}$  doped to  $5x10^{19}$  cm<sup>-3</sup> and  $1\mu$  m SiGe<sub>0.1</sub>/SiGe<sub>0.15</sub>C<sub>0.005</sub>. Finally, the sample was capped with 250nm SiG $\phi_1$ , doped to approximately  $2x10^{20}$  cm<sup>-3</sup>. The SiGe/Si micro-coolers are fabricated with standard silicon integrated circuit technology. The cooler device areas were defined by etching mesas down to the SiGe buffer layer. Ti/Al/Ti/Au metallisation was made on top of the mesa and on the SiGe buffer layer next to the mesa for top and bottom contacts respectively. The size of the sample is ranging from 50x50μm to 100x100μm. Figure. 1 shows a scanning electron micrograph picture of this device.

<sup>&</sup>lt;sup>1</sup>Electrical Engineering Dept. of University of California, Santa Cruz, CA 94056,

<sup>&</sup>lt;sup>2</sup>Electrical and Computer Engineering Dept. of University of California, Santa Barbara, CA 93106;

<sup>&</sup>lt;sup>3</sup>HRL laboratories, LLC Malibu, California 90265

Figure 1 The SEM picture of SiGe superlattice microcooler integrated with heater sensor

First resistance versus temperature of the heater sensor was calibrated. Four-wire measurement was used to reduce the effect of contact wires and pads. Then at a given heater power (fixed top layer temperature,  $T_{\rm h}$ ), the voltage difference across the device  $\Delta V$  was measured. The bottom of the silicon substrate was maintained at the heat sink temperature ( $T_{\rm s}$ ). It is important to note that the measured thermoelectric voltage  $\Delta V$  has a contribution from both the superlattice Seebeck coefficient and also the Si substrate Seebeck coefficient.

$$\Delta V = S1 \times (T_s' - T_s) + S2 \times (T_h - T_s')$$

(Eqn. 2)

S1 is the Seebeck coefficient of bulk Silicon;  $T_s$ ' is the temperature at the interface between the superlattice layer and substrate. If the temperature  $T_s$ ' is equal to  $T_s$ , then the effective Seebeck coefficient equals to that of superlattice. However, this is not the case for our devices. We will see that the superlattice Seebeck coefficient S2 could be easily derived by analyzing experimental results for different thin film layer thicknesses and device sizes. Bao Yang et al.have used AC method to measure Seebeck coefficient of thin films  $^{13}$ , the signal of our samples are large enough for an accurate DC measurements.

**Figure 2** Cross-section schematic of superlattice device (not to scale)

### **Results and Discussion**

The heater resistance changes linearly with temperature near 300K, so it was used as a temperature sensor on top of the superlattice device. The temperature sensor was

calibrated by measuring the resistance with very low excitation currents at different ambient temperatures. Variations of the resistance with temperature could be fitted well with a line, with an error less than 0.02%. The heater samples used in this experiments have an average of  $4x10^3$

$${}^{0}\text{C}$$

in a unit resistance  $(\frac{dR/dT}{R})$ . Subsequently

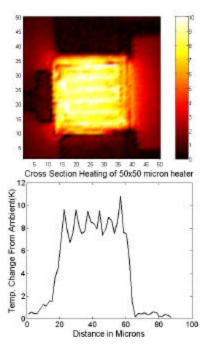

thermoreflectance imaging was used to measure the temperature distribution on top of the device when the heater was on. As it can be seen from Fig. 3, the heating was localized on top of the thin film device.

**Figure 3** Demonstration of localized heating of SiGe superlattice micro coolers

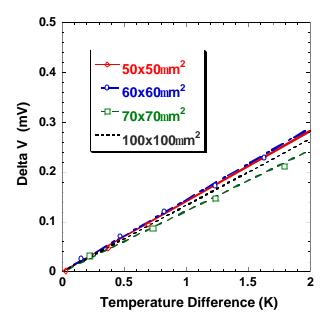

Figure 4 displays the voltage change across the sample as a function of the temperature gradient for all different size samples, ranging from  $50x50\mu m$  to  $100x100\mu m$ . The slope of the curve is the average Seebeck coefficient with contribution from superlattice and silicon substrate It is known that seebeck coefficient is geometry independent therm odynamic property. This corresponds with the results in Figure 4, which shows size independent of effective seebeck coefficient. Table 1 summarizes the thermoelectric voltage measured in the experiments. It shows the sample  $SiGe_{0.2}$ :B with 3um superlattice thickness and doping concentration of  $57x10^{19}$  cm<sup>-3</sup> has an average Seebeck coefficient of  $135.4\mu V/^{0}C$ .

**Figure 4** Thermoelectric voltage versus temperature difference between top of the device and bottom contact

| Sample size<br>(µmxµm) | Effective Seebeck coefficient (μV <sup>ρ</sup> C) |  |  |

|------------------------|---------------------------------------------------|--|--|

| 50x50                  | 138 <u>+</u> 0.1                                  |  |  |

| 60x60                  | 140.0 <u>+</u> 1.0                                |  |  |

| 70x70                  | 131.0 <u>+</u> 0.6                                |  |  |

| 100x100                | 132.4 <u>+</u> 1.0                                |  |  |

| Average                | 135.4                                             |  |  |

Table 1  $Si_{0.7}Ge_{0.3}$  superlattice microcooler Seebeck coefficient data for different size samples

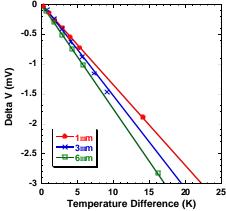

Venkatasubramanian's recent paper in Nature<sup>2</sup> reported the cooling performance is related to the thickness of the superlattice layer. To further investigate the influence of different superlattice thickness on the device property. We also measured the thermoelectric voltage for different superlattice thickness, 1um, 3um, and 6um. The results were illustrated in . It can be seen that thicker the superlattice higher the measured thermoelectric voltage thickness,  $135 \mu V ^{0}C$ ,  $154 \mu V ^{0}C$  and  $174 \mu V ^{0}C$  for  $1 \mu m$ ,  $3 \mu m$  and  $6 \mu m$ superlattice respectively. The increase of the thermoelectric voltage is due to the increase in the thermal resistance of the thin film device with respect to the substrate as superlattice becomes thicker. As illustrated in Figure 6 simplified thermal model of superlattice micro-cooler device, from the equation of

$$R_{th} = \frac{1}{b_{th}} * \frac{d}{A}$$

(Eqn.3)

it is obvious to see  $R_{th}(SL)$ : thermal resistance superlattice is proportional to the uperlattice thickness  $d_{sl}$ . The change of  $R_{th}(SL)$  directly influences T  $_s$ ':

$$Ts' = Ts + \frac{R_{th}(Si)}{R_{th}(Si) + R_{th}(SL)} * \Delta T$$

(Eqn. 4)

And it causes the change of effective seebeck coefficient:  $S=[S2*(Th-T_s')+S1*(T_s'-T_s)]/DT$  (Eqn.5)

Figure 5 Comparison of seebeck coefficient with different superlattice thickness (fitted)

$$\Delta \mathbf{V}, \Delta \mathbf{T} \underbrace{ \begin{array}{c} \mathbf{T_h} \\ \mathbf{SL} \ (\mathbf{S2}) \\ \end{array}}_{\mathbf{Si} \ \mathbf{Substrate} \ (\mathbf{S1}) } \mathbf{T}_s^{\underbrace{+}} \underbrace{ \begin{array}{c} \mathbf{R_n} (\mathbf{SL}) \\ Ts' = Ts + \frac{\rho_n (\mathbf{SL})}{\rho_n (\mathbf{S}) + k_n (\mathbf{SL})} * \Delta T \\ \end{array}}_{\mathbf{T_s} } * \Delta T$$

$$\mathbf{T}_s$$

$$R_{th} = \underbrace{\Delta T}_{\mathcal{Q}} = \underbrace{\frac{1}{\rho_{th}} * \frac{d}{A}}_{}$$

R<sub>th</sub> thermal resistance,β<sub>th</sub> thermal conductivity; d: thickness; A: area

Figure 6 Simplified thermal model of superlattice microcooler (This model assumes the thermal resistance of the  $SiN_x$  and buffer layer is much smaller than the thermal resistance of the superlattice layer)

To calculate the actual Seebeck coefficient of superlattice, we need to know the Ts, which is related with the thermal resistance of the device. In this calculation, thermal resistance was obtained experimentally by using equation:  $R_{th} = \frac{\Delta T}{Q}$  (Eqn. 6),  $\Delta T$  is the temperature difference created, Q is the heat load on top of the device. The thermal resistance for a 100x100um<sup>2</sup> device based on bulk silicon R<sub>th</sub>(Si) was 157.0 K/W, the measured thermal resistance of the device with different superlattice thickness were listed in Table 2. From the known of thermal resistance of bulk Silicon and that of the overall (superlattice+substrate), the T<sub>s</sub> - T<sub>s</sub> could be calculated by Eqn.4 assuming a temperature change of 10K. The  $\Delta V$  of the device could be obtained by its effective Seebeck cofficient. Then a pure superlattice of this structure S2 could be calculated by Eqn.2 with all the known dat a.

Table 2 lists all the calculation results and it showed an average seebeck coefficient of this structure superlattice is around 217.6  $\mu V/^0 C$ .

| SL thickness | R <sub>th</sub>          | $\Delta V$ | $T_s$ '- $T_s$ | S (SL)              |  |

|--------------|--------------------------|------------|----------------|---------------------|--|

|              | (Device)                 | (mV)       | (K)            | $(\mu V/^{0}C)$     |  |

|              | (K/W)                    |            |                |                     |  |

| 1um          | 215.1                    | 1.28       | 7.30           | 229.6 <u>+</u> 10.0 |  |

| 3um          | 322.3                    | 1.54       | 4.87           | 205.3 <u>+</u> 10.5 |  |

| бum          | 422                      | 1.68       | 3.72           | 217.8 <u>+</u> 8.2  |  |

| Ave.         |                          |            |                |                     |  |

| SL seebeck   |                          |            |                |                     |  |

| coefficient  | 217.6 μV/ <sup>0</sup> C |            |                |                     |  |

**Table 2** Calculation of superlattice thickness (Sample size 100x100µm)

#### **Conclusions**

We showed that the integrated heater sensor on top of the thin films provides a convenient method to characterize the Seebeck of SiGe superlattice material. This will help further development and improvement of the performance of SiGe superlattice coolers.

Seebeck coefficient of  ${\sim}217\mu\text{V/K}$  was measured for Si/SiGe superlattice p-doped to  $5\times10^{19}\text{cm}^{-3}$ . The experimental results were verified by obtaining consistent results with various superlattice thickness (1-6um) and device sizes (2,500-10,000  $\mu\text{m}^2$ ).

#### Acknowledgements

This work was supported by the DARPA HERETIC program and the Army Research Office.

# Reference

\_

<sup>10</sup> T. Yao, Appl. Phys. Lett. 51, 1798 (1987).

<sup>11</sup> Xiaofeng Fan etc. Applied Physics Letters, Vol. 78, No.11, 12 March 2001.

<sup>12</sup> CRC Handbook of Thermoelectrics, ed. by D.M. Rowe (CRC Press, Boca Raton, FL, 1995)

<sup>15</sup> Bao Yang et. al. "Characterization of cross-plane thermoelectric properties of Si/Ge Superlattices" Proceeding of 20<sup>th</sup> International Conference on Thermoelectrics (2001)

<sup>&</sup>lt;sup>1</sup> Xiaofeng Fan etc. Applied Physics Letters, Vol. 78, No.11, 12 March 2001.

<sup>&</sup>lt;sup>2</sup> Rama Venkatasubramanian et. al. "Thin-film thermoelectric devices with high room-termperature figures of merit", P597 Vo. 413, October 11 <sup>th</sup>, 2001, Nature <sup>3</sup> Xiaofeng Fan et. al. "Integrated Cooling for Si-based Microelectronics", International conference on Thermoelectrics, June 2001

<sup>&</sup>lt;sup>4</sup> Xiaofeng Fan et. al. "High cooling power density SiGe/Si micro coolers" Elec. Lett., Vol. 37, No. 2, 18 January 2001 <sup>5</sup> T. Borca-Tasciuc et.al. Superlattices and Microstructure 28, 199 (2000)

<sup>&</sup>lt;sup>6</sup> R. Venkatasubramanian, Phys. Rev. B 61, 3091 (2000)

<sup>&</sup>lt;sup>7</sup> H. Beyer, et al Proc. 18<sup>th</sup> Int. Conf. Thermoelectrics, ICT'99, 687 (1999)

<sup>&</sup>lt;sup>8</sup> R. Venkatasubramanian, Recent Trends in Thermoelectric Materials Research III, T. M. Tritt, Ed., Academic Press 71, 196 (2001)

<sup>&</sup>lt;sup>9</sup> W. L. Liu et. al. J. Nanosci. And Nanotech. 1, 37 (2001)