## High Cooling Power Density of SiGe/Si Superlattice Microcoolers

Gehong Zeng, Xiaofeng Fan, Chris LaBounty, John E. Bowers, Edward Croke<sup>1</sup>, James Christofferson<sup>2</sup>, Daryoosh Vashaee<sup>2</sup>, Yan Zhang<sup>2</sup>, and Ali Shakouri<sup>2\*</sup> Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

<sup>1</sup> HRL Laboratories, LLC, Malibu, California, 90265

<sup>2</sup> Baskin School of Engineering, University of California, Santa Cruz, CA 95064

### ABSTRACT

Fabrication and characterization of SiGe/Si superlattice microcoolers integrated with thin film resistors are described. Superlattice structures were used to enhance the device performance by reducing the thermal conductivity, and by providing selective emission of hot carriers through thermionic emission. Thin film metal resistors were integrated on top of the cooler devices and they were used as heat load for cooling power density measurement. Various device sizes were characterized. Net cooling over 4.1 K and a cooling power density of 598 W/cm<sup>2</sup> for 40 × 40  $\mu$ m<sup>2</sup> devices were measured at room temperature.

### **INTRODUCTION**

With the rapid development of VLSI technology, heat generation and thermal management are becoming one of the barriers to further increase clock speeds and decrease feature sizes. There has been an increasing demand for localized cooling and temperature stabilization of optoelectronic devices. Thermoelectric (TE) coolers based on bulk BipTe<sub>3</sub> are commonly used for electronic and optoelectronic device cooling, but they cannot be directly integrated with the IC fabrication process. Recently ptype BiTe/SbTe thin film coolers have been demonstrated with high thermoelectric figure-of-merit and cooling power density<sup>1</sup>. Si-based microcoolers are attractive for their potential monolithic integration with Si microelectronics. SiGe is a good thermoelectric material especially for high temperature applications<sup>2,3</sup>, and superlattice structures can further enhance the cooler performance by reducing the thermal conductivity between the hot and the cold junctions, and by selective emission of hot carriers above the barrier layers in the thermionic emission process<sup>4-19</sup>. SiGe/Si superlattice structures were grown on Si substrates using molecular beam epitaxy (MBE). Thin film resisters were integrated with the cooler devices. It shows the possibility to monolithically integrate these coolers with Si-based microelectronic devices for localized cooling and temperature stabilization.

#### **EXPERIMENTAL DETAIS**

The structure of the microcooler samples consisted of a 3  $\mu$ m thick 200 × (5nm Si<sub>0.7</sub>Ge<sub>0.3</sub>/10nm Si) superlattice grown symmetrically strained on a buffer layer designed so that the in-plane lattice constant was approximately that of relaxed Si<sub>0.8</sub>Ge<sub>0.2</sub>. The doping level is  $5\times10^{19}$  cm<sup>-3</sup> for both the superlattice and the buffer layer. A 0.5  $\mu$ m Si<sub>0.9</sub>Ge<sub>0.1</sub> cap layer was grown on the superlattice with the top 0.25  $\mu$ m doped to  $2 \times 10^{20}$  cm<sup>-3</sup> for device ohmic contact. This Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si superlattice has a valance band offset of about 0.2 eV, and hot holes over this barrier produce thermionic cooling. In addition, superlattice structure has many interfaces that

<sup>\*</sup> ali@soe.ucsc.edu

increase phonon scattering, and therefore lower thermal conductivity. The samples were grown with MBE on five inch diameter (001)-oriented Si substrates, doped to  $0.001 \sim 0.006 \ \Omega$ -cm with Boron.

Mesas 0.6  $\mu$ m high were formed using reactive ion etching down to the SiGe/Si superlattice layer. 100 nm titanium layer was deposited to form a titanium silicide on the Silicon surface and to act as a metal barrier to separate SiGe and Al. Subsequently 1 $\mu$ m thick aluminum layer was deposited. To facilitate wire bonding, additional metal layers of titanium and gold were used. Annealing was done at a temperature of 450 °C for 5 seconds.

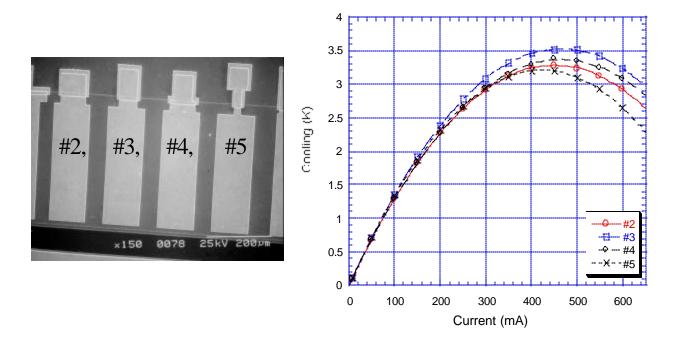

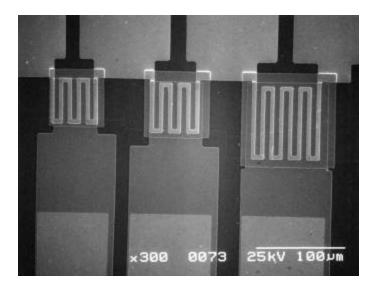

In order to facilitate integration of thin film resistor on top of the device, the metal contact to the cold junction was extended to the side with 0.3 micron thick  $SiN_x$  insulating layer underneath (see Fig. 1). In this single element cooler configuration, heat flow to the cold junction from the electrode pad has to be taken into account, and the pad width can be optimized to get a balance between heat conduction to the substrate and the resistive Joule heating in the metal layer. Coolers with various side pad widths were characterized for this purpose. Fig. 1a shows the scanning electron micrograph (SEM) of devices with an area of 6400  $\mu$ m<sup>2</sup> which have different side pad widths. Fig. 1b shows the measured cooling on top of the device versus applied current. It can be seen that device #3 has the best performance. With further processing a thin film metal resister was integrated on top of the device and used as a thermal load for cooling power density measurement. An SEM image of the processed devices with the heater is shown in Fig. 2.

Fig. 1 (a) Devices with an area of 6400  $\mu$ m<sup>2</sup> and with different side pad widths. (b) Measured cooling on top of the device versus current.

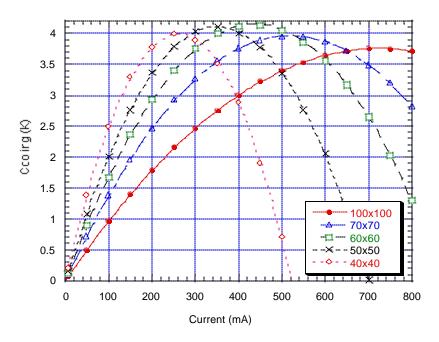

Devices were tested at room temperature. Device cooling was measured using two micro thermocouples, one thermocouple bead size ~50 micron was placed on top of the cooler and

another one on the substrate far away from the device. Fig. 3 shows the test results for coolers (processed without the heater on top) ranging in size from  $40 \times 40 \ \mu\text{m}^2$  to  $100 \times 100 \ \mu\text{m}^2$ . The maximum cooling of about 4.1 K was measured for the  $60 \times 60 \ \mu\text{m}^2$  device.

Fig. 2 Processed SiGe/Si coolers with integrated thin film metal wire resisters.

Fig. 3 Cooling measured on top of the device versus current for  $40 \times 40 \,\mu\text{m}^2$ ,  $50 \times 50 \,\mu\text{m}^2$ ,  $60 \times 60 \,\mu\text{m}^2$ ,  $70 \times 70 \,\mu\text{m}^2$  and  $100 \times 100 \,\mu\text{m}^2$  SiGe/Si coolers.

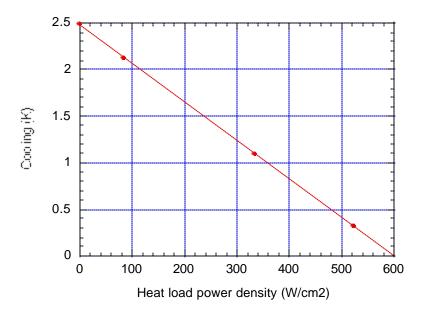

The integrated thin film wire resister was used as a heater. A constant electric current was applied through the metal wire to provide a constant heat load while the cooling with this thermal

load was measured. The maximum cooling power is defined as the heat load power density that makes the device's maximum cooling temperature equal to zero. Fig. 4 shows that the cooling versus heat load power density for  $40 \times 40 \ \mu m^2$  device. It can be seen that this device has a maximum cooling power density of 598 W/cm<sup>2</sup> at room temperature.

Fig. 4 Measured cooling power density for 40  $\times$  40  $\mu m^2$  SiGe/Si cooler at room temperature.

#### DISCUSSION

According to conventional bulk thermoelectric cooler models, the maximum cooling is determined by the TE figure-of-merit and is independent of the cooler size. However, with the device minimization the cooler thermal and electrical resistances both become very small and non-ideal effects, such as metal-semiconductor contact resistance and heat sink thermal resistance, must be considered in the device modeling. These non-ideal effects not only reduce the maximum cooling but also make the cooling performance device size dependent. For example, the cooler thermal resistance is inversely proportional to the cooler area, while the thermal resistance of the silicon substrate beneath the device is inversely proportional to the square root of the cooler area $^{20,21}$ . The ratio of the cooler thermal resistance to the substrate (heat sink) thermal resistance increases with decreasing the device size. Therefore as the device gets smaller, substrate becomes closer to an ideal heat sink and the overall micro refrigerators cooling performance improves. Another difference from conventional bulk TE coolers is that the thin film microcoolers characterized here are single element devices instead of the p- and n-type array structures. One should consider heat conduction from side contact to the cold junction of the device. For the cooler structures in this paper, the side contact scales with the linear dimension of the cooler. Thus larger devices tend to be less affected by the heat conduction from side contact and also by the fixed thermal load of the thermocouple on top of the device. Because of all the non-ideal effects, there is an optimal device size for the microcooler, which is shown in the measurements in Fig. 3 where  $60 \,\mu\text{m} \times 60 \,\mu\text{m}$  devices have the largest cooling.

## CONCLUSION

Thin film resister wires were integrated into the cooler devices, which were used as controllable electric thermal loads. A cooling power density of 598 W/cm<sup>2</sup> for coolers of  $40 \times 40$   $\mu$ m<sup>2</sup> and cooling up to 4.1 K for coolers of  $60 \times 60 \mu$ m<sup>2</sup> were measured at room temperature. With standard IC processing technology, thin film metal wire resisters were integrated into the cooler devices which are used as electric thermal load to the coolers. This shows the possibility of monolithic integration of devices with micro thin film coolers.

## ACKNOWLEDGMENTS

This work was supported by the DARPA HERETIC program and the Army Research Office and the content of the information does not necessarily reflect the position or the policy of the federal government, and no official endorsement should be inferred.

# REFERENCES

- <sup>1</sup> R. Venkatasubramanian, E. Siivola, T. Colpitts, and B. O'Quinn, Nature **413**, 597-602 (2001).

- <sup>2</sup> H. J. Goldsmit, *Thermoelectric Refrigeration* (Plenum, New York, 1964).

- <sup>3</sup> J. B. Vining, J. Appl. Phys. **69**, 331-341 (1991).

- <sup>4</sup> A. Shakouri and J. E. Bowers, in The 16th International Conference on Thermoelectrics, Dresden, Germany, 26-29 Aug. 1997, p. 636-40.

- <sup>5</sup> A. Shakonri, C. LaBounty, P. Abraham, J. Piprekt, J. E. Bowers, in The Next Generation Materials for Small-Scale Refrigeration and Power Generation Applications Symposium, Boston, MA, USA 30 Nov.-3 Dec. 1998, p. 449-58.

- <sup>6</sup> A. Shakouri and J. E. Bowers, Applied Physics Letters **71**, 1234-6 (1997).

- <sup>7</sup> C. B. Vining and G. D. Mahan, Journal of Applied Physics **86**, 6852-3 (1999).

- <sup>8</sup> A. Shakouri, C. LaBounty, J. Piprek, P. Abraham, and J. E. Bowers, Applied Physics Letters **74**, 88-9 (1999).

- <sup>9</sup> L. D. Hicks, T. C. Harman, and M. S. Dresselhaus, Applied Physics Letters **63**, 3230-2 (1993).

- <sup>10</sup> T. Koga, X. Sun, S. B. Cronin, and M. S. Dresselhaus, Applied Physics Letters **73**, 2950-2 (1998).

- <sup>11</sup> T. Koga, X. Sun, S. B. Cronin, and M. S. Dresselhaus, Applied Physics Letters **75**, 2438-40 (1999).

- <sup>12</sup> T. Koga, S. B. Cronin, M. S. Dresselhaus, J. L. Liu, and K. L. Wang, Applied Physics Letters **77**, 1490-2 (2000).

- <sup>13</sup> F. Xiaofeng, Z. Gehong, C. LaBounty, J. E. Bowers, E. Croke, C. C. Ahn, S. Huxtable, A. Majumdar, and A. Shakouri, Applied Physics Letters **78**, 1580-2 (2001).

- <sup>14</sup> F. Xiaofeng, Z. Gehong, E. Croke, G. Robinson, C. LaBounty, A. Shakouri, J. E. Bowers, in The 7th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Las Vegas, NV, USA 23-26 May 2000, p. 304-7.

- <sup>15</sup> Z. Gehong, A. Shakouri, C. L. Bounty, G. Robinson, E. Croke, P. Abraham, F. Xiafeng, H. Reese, and J. E. Bowers, Electronics Letters **35**, 2146-7 (1999).

- <sup>16</sup> H. J. Osten, Journal of Applied Physics **84**, 2716-21 (1998).

- <sup>17</sup> B. L. Stein, E. T. Yu, E. T. Croke, A. T. Hunter, T. Laursen, A. E. Bair, J. W. Mayer, and C. C. Ahn, in The 24th Conference on the Physics and Chemistry of Semiconductor Interfaces Research, Triangle Park, NC, USA 12-15 Jan. 1997, p. 1108-11.

- <sup>18</sup> C. LaBounty, A. Shakouri, G. Robinson, P. Abraham, and J. E. Bowers, in The 18th International Conference on Thermoelectrics, Baltimore, MD, USA 29 Aug.-2 Sept. 1999, p. 23-6.

- <sup>19</sup> C. LaBounty, A. Shakouri, and J. E. Bowers, Journal of Applied Physics **89**, 4059-64 (2001).

- <sup>20</sup> L. Coldren and S. Corzine, Diode Lasers and Photonic Integrated Circuits (John Wiley & Sons, Inc., New York, 1995).

- <sup>21</sup> C. LaBounty, Ph. D. Thesis, University of California, Santa Barbara, 2001.