# ECE695A: Reliability Physics of Nano-Transistors Lecture 23: Characterization of Defects Responsible for TDDB

Muhammad Ashraful Alam alam@purdue.edu

#### Copyright 2013

This material is copyrighted by M. Alam under the following Creative Commons license:

Attribution-NonCommercial-ShareAlike 2.5 Generic (CC BY-NC-SA 2.5)

Conditions for using these materials is described at

http://creativecommons.org/licenses/by-nc-sa/2.5/

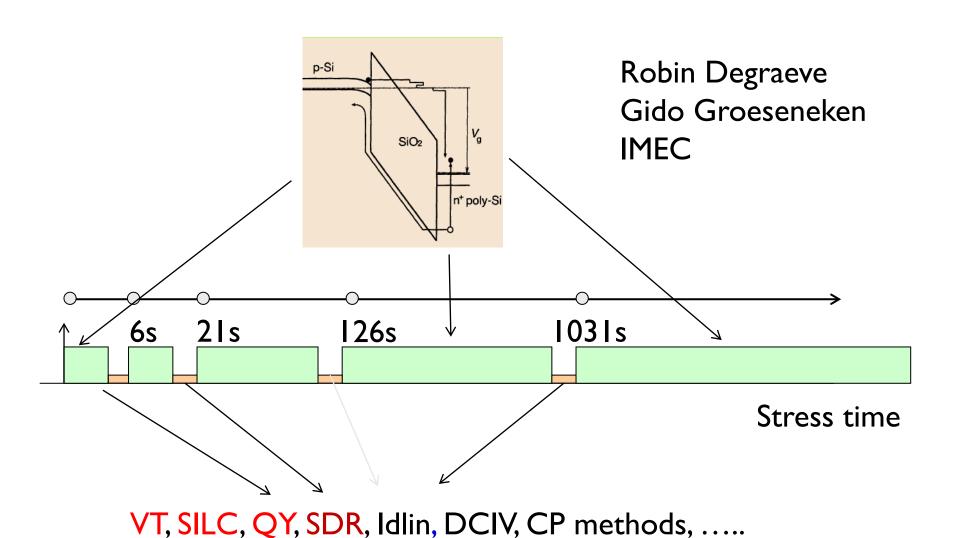

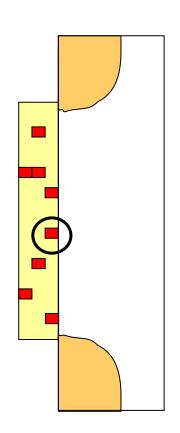

#### Measurement of bulk oxides

Alam ECE-695

#### Measurement of bulk traps

#### VT Method and Trap Coloring

#### **Outline**

- I. Background: Measurement of bulk traps

- 2. Shift in Threshold Voltage and C-V Method

- 3. Stressed induced leakage current (SILC) method

- 4. Quantum Yield Experiments

- 5. Conclusions

### Gate Oxide Breakdown: SiO<sub>2</sub> on Planar Si

Alam, IRPS, 2000; ECS, 2000; Stathis, IBM J. Res/Dev, 46, 2002.

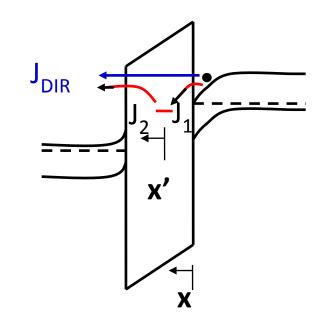

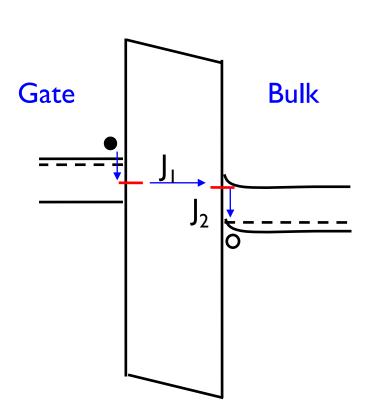

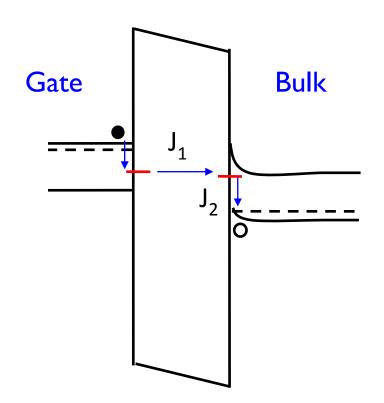

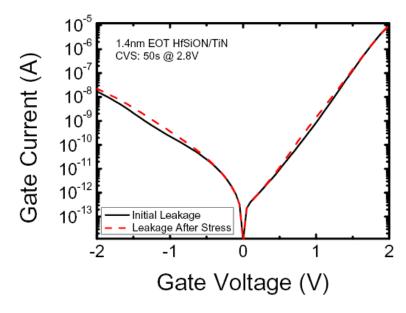

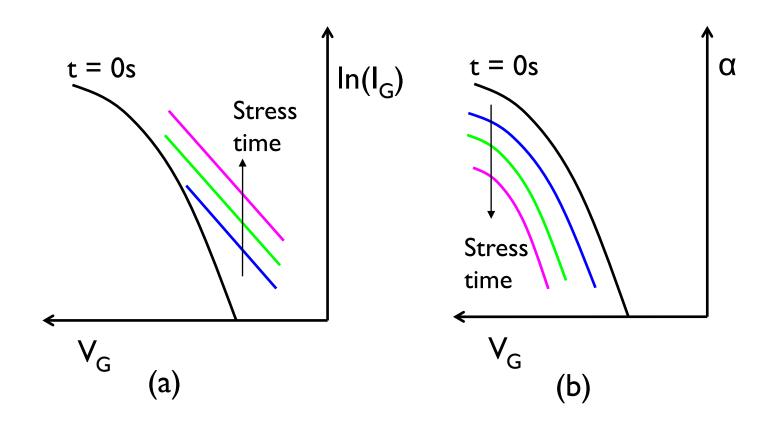

The low voltage leakage part is defined by half the slope of typical  $I_G$ - $V_G$  curves !

$$\begin{split} \boldsymbol{J}_{dir} &= \boldsymbol{A} \boldsymbol{P}_{dir} \left[ f_C \left( 1 - f_A \right) - f_C \left( 1 - f_A \right) \right] \\ &= \boldsymbol{A} \boldsymbol{P}_{dir} \left( f_C - f_A \right) \end{split}$$

$$J_{1} = c\sigma N_{OT} P_{1} \left[ f_{c} \left( 1 - f_{T} \right) - f_{T} \left( 1 - f_{C} \right) \right]$$

$$J_1 = c\sigma N_{OT} \frac{P_1}{f_1} (f_C - f_T)$$

$$J_2 = c\sigma N_{OT} P_2 \left( f_T - f_A \right)$$

$$J_{SILC} = c\sigma N_{OT} \frac{P_1 P_2}{P_1 + P_2} (f_C - f_A)$$

$$P(x) \Box e^{-\int_{0}^{x} k(x) dx}$$

$$J_{dir} = AP_{dir} \left( f_C - f_A \right) \qquad J_{SILC} = c\sigma$$

$$P_{DIR} = \exp\left( -\int_0^{T_{cx}} k(x) dx \right) \qquad \sim c\sigma$$

$$= \exp\left( -\int_0^{\xi T_{cx}} k(x) dx \right) \times \exp\left( -\int_0^{\xi T_{cx}} k(x') dx' \right)$$

$$\frac{P_1 P_2}{P_1 + P_2} = \frac{\exp\left( -\int_0^{\xi T_{cx}} k(x) dx \right) \times \exp\left( -\int_0^{\xi T_{cx}} k(x') dx' \right)}{\exp\left( -\int_0^{\xi T_{cx}} k(x) dx \right) + \exp\left( -\int_0^{\xi T_{cx}} k(x') dx' \right)}$$

$$= P_{dir} \times \left[ \exp\left( -\int_0^{\xi T_{cx}} k(x) dx \right) + \exp\left( -\int_0^{\xi T_{cx}} k(x') dx' \right) \right]^{-1}$$

$$J_{SILC} = c\sigma N_{OT} \frac{P_1 P_2}{P_1 + P_2} (f_C - f_A)$$

$$\sim c\sigma N_{OT} P (f_C - f_A)$$

$$\stackrel{dx}{=} \begin{bmatrix} P_1 + P_2 & P_2 \\ x \end{bmatrix}$$

$$x = 0 \quad \text{Trap loc.} \quad x = T_{OX}$$

11

Alam ECE-695

$$J_{SILC} = \frac{c\sigma N_{OT} P}{2} (f_C - f_A)$$

$$J_{DIR} = AP^2 \left( f_c - f_a \right)$$

$$\boldsymbol{J}_{SILC} = \frac{c\sigma N_{OT}}{2} \sqrt{\frac{\left(f_{C} - f_{A}\right)}{A}} \sqrt{\boldsymbol{J}_{DIR}}$$

$$\ln\left(J_{SILC}\right) = \ln\left(\frac{c\sigma N_{OT}(t)}{2}\sqrt{\frac{\left(f_{C} - f_{A}\right)}{A}}\right) + \frac{1}{2}\ln\left(J_{DIR}\right)$$

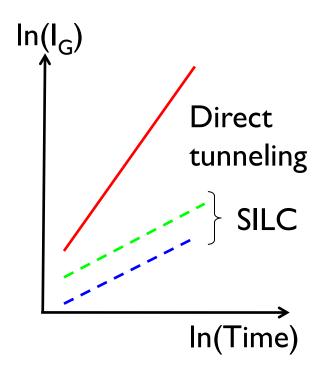

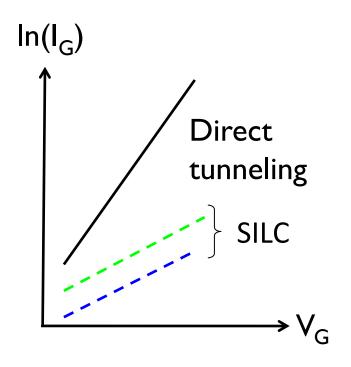

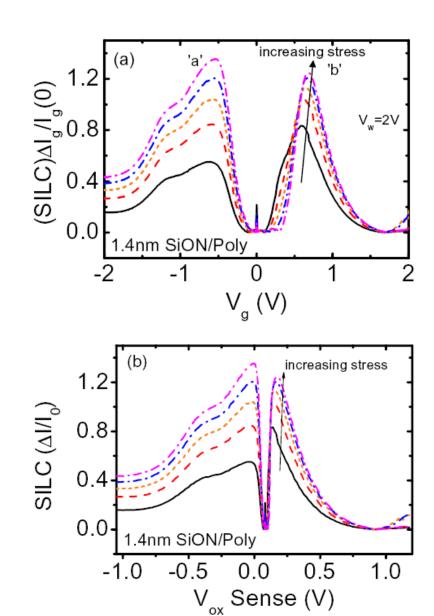

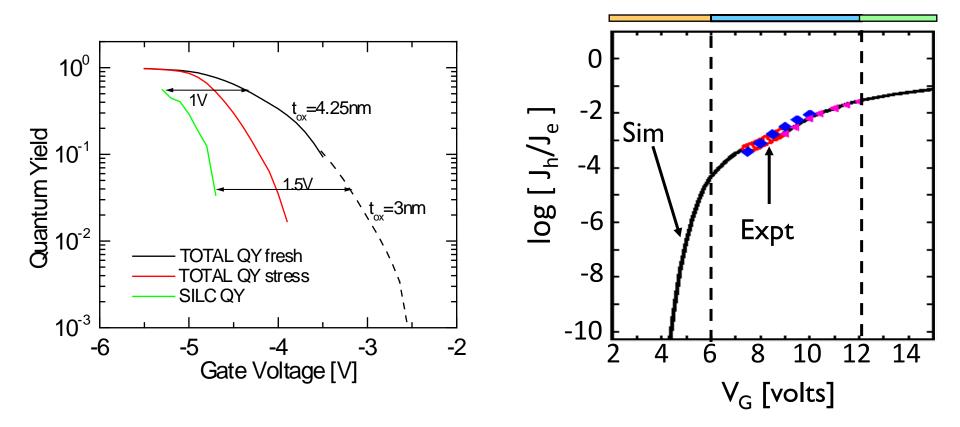

Stress induced leakage current has half the slope of direct tunnelingcentrent

### I<sub>G</sub>-V<sub>G</sub> Slope of SILC vs. Direct Tunneling

Individual current components

Total current

#### Native Traps: VG Dependence

#### Low Voltage Stress Induced Leakage (LV-SILC)

$$J_{1} = c\sigma N_{OT} P_{DIR} \left( f_{C} - f_{T} \right)$$

$$\boldsymbol{J}_2 = \frac{N_{OT} f_T}{\tau_R} (1 - f_A)$$

15

Alam ECE-695

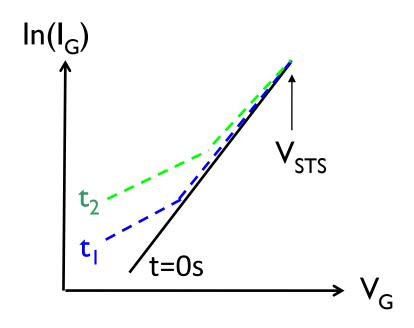

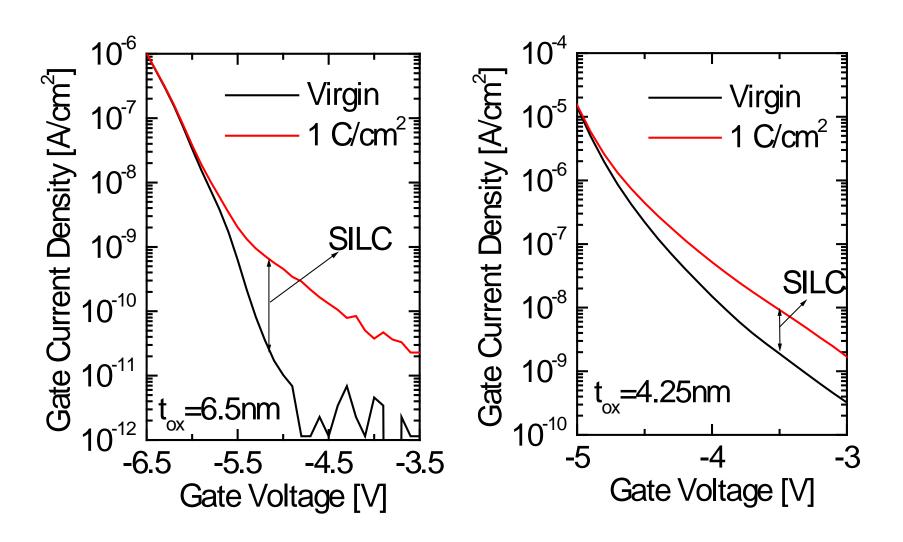

#### Classical SILC and low-voltage SILC

In very thin oxides, classical SILC may always be undetectable

Bias it so that  $J_{dir}$  is suppressed

#### Low-voltage SILC (LV-SILC)

O'Conner et al., IRPS, 2008.

Alam ECE-695

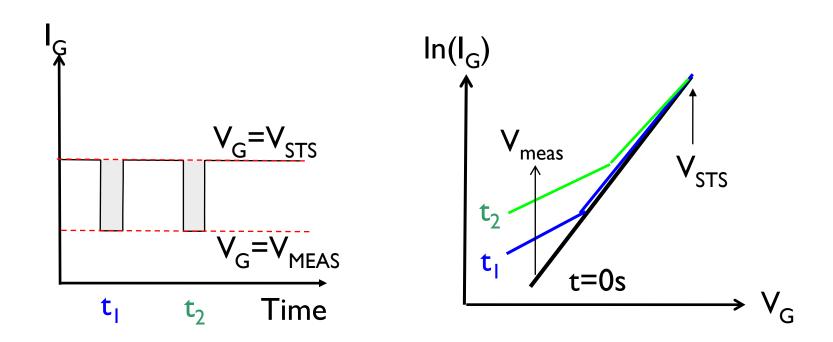

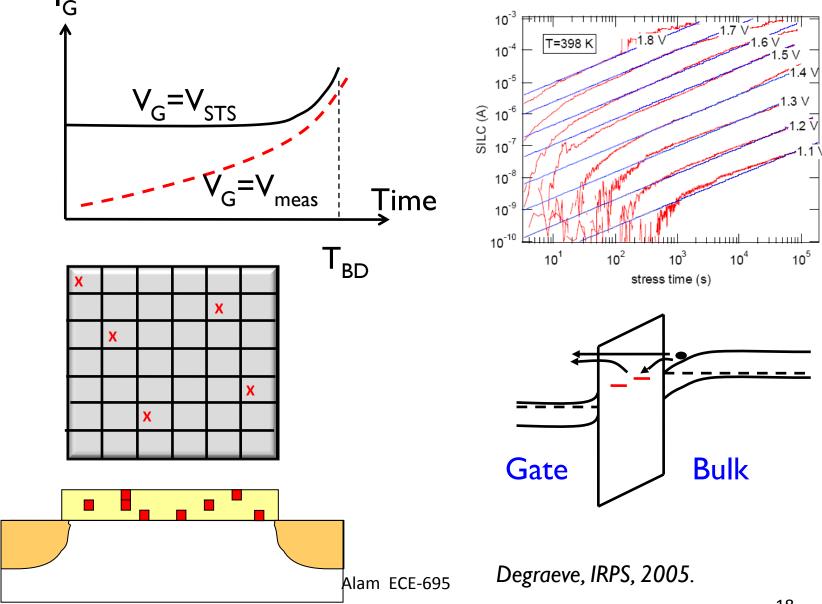

#### Gate Leakage at Low Voltages (SILC)

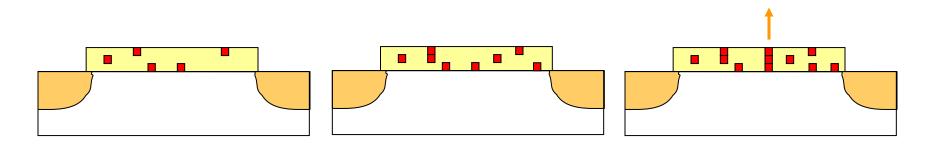

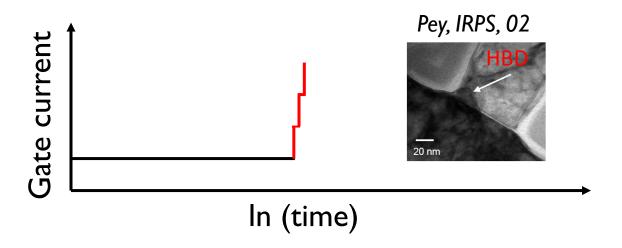

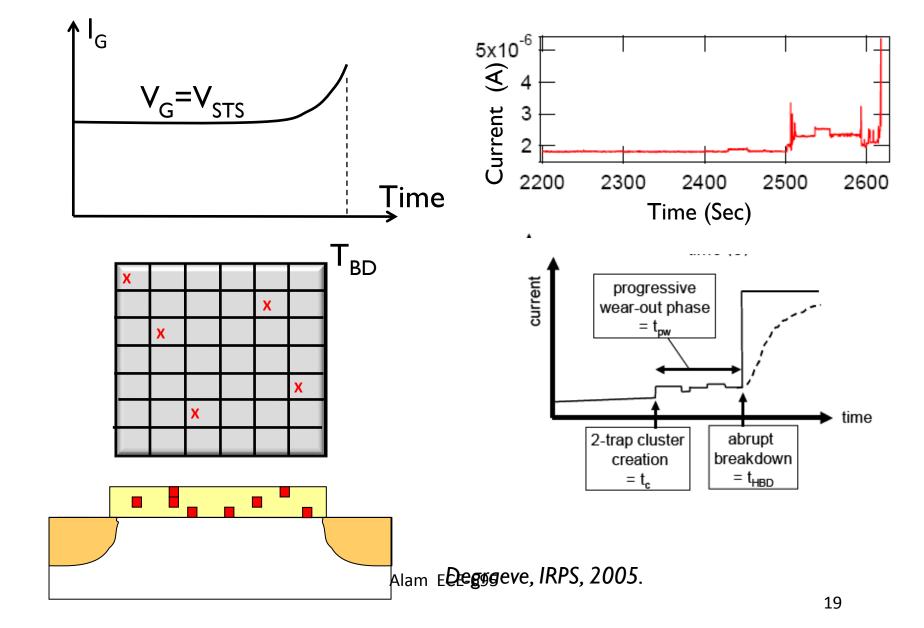

#### Gate Leakage Fluctuation at Breakdown

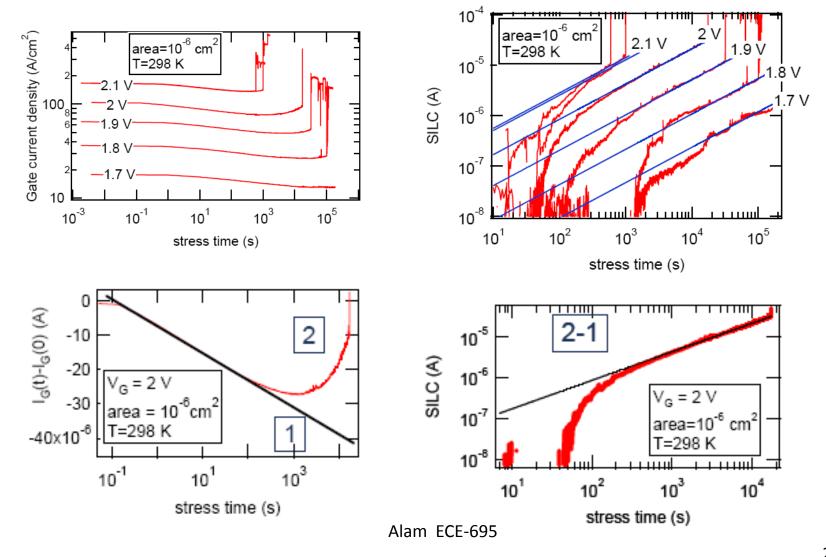

## Precaution: log-t Trapping must be subtracted

#### **Outline**

- I. Background: Measurement of bulk traps

- 2. Shift in Threshold Voltage and C-V Method

- 3. Stressed induced leakage current (SILC) method

- 4. Quantum Yield Experiments

- 5. Conclusions

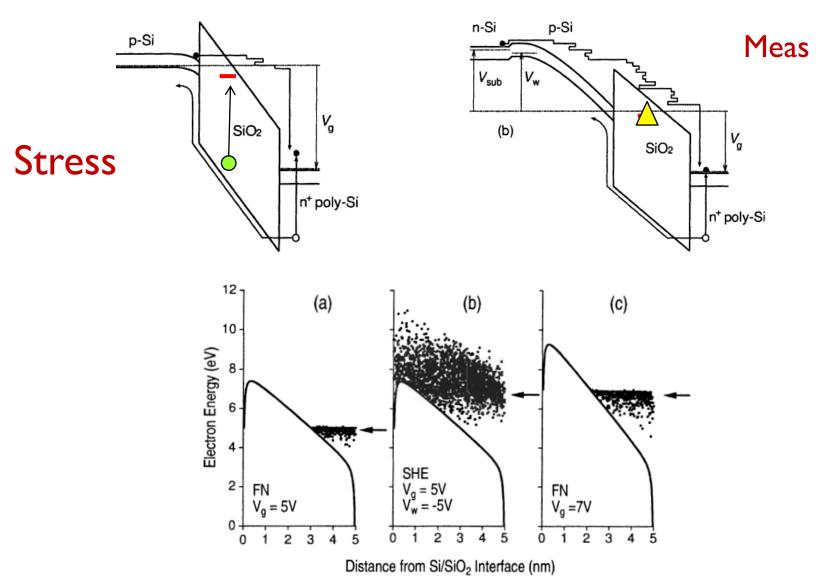

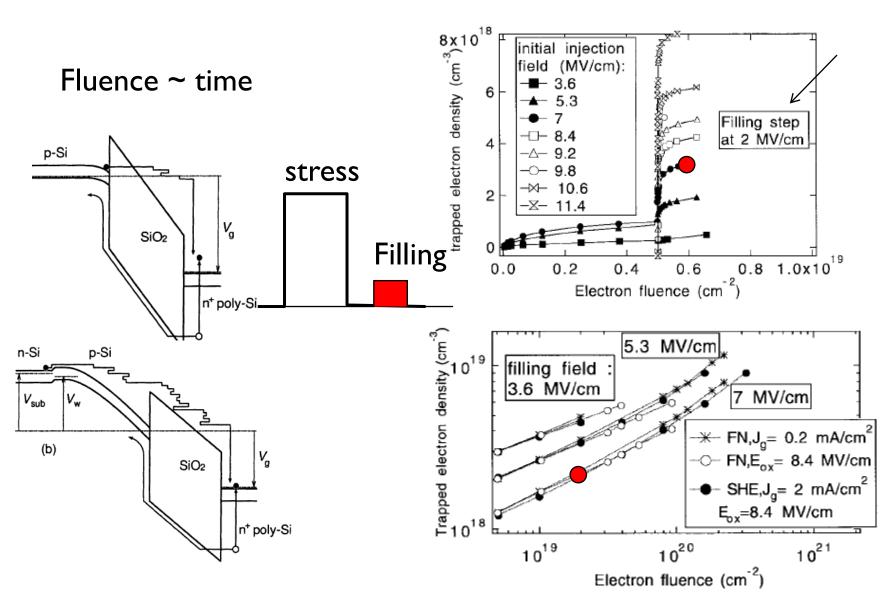

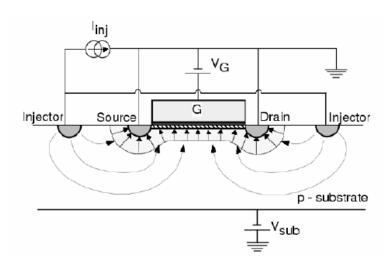

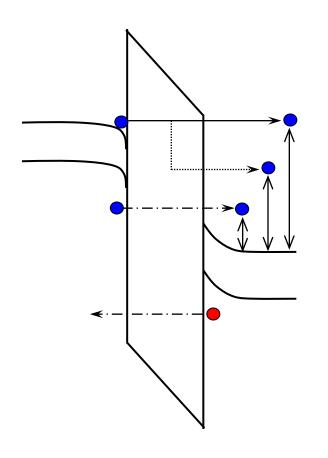

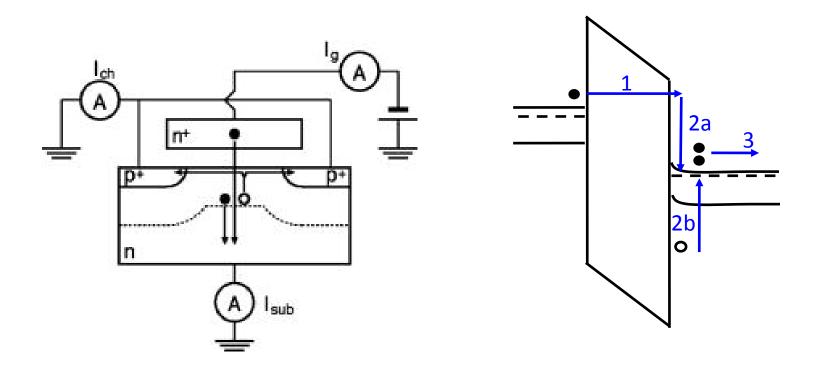

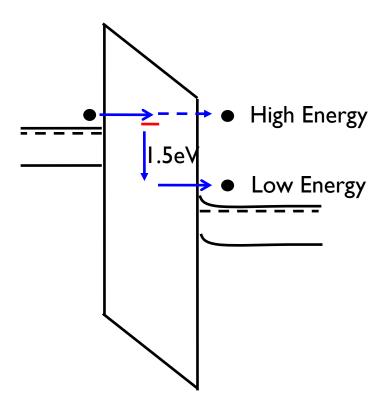

#### What is the energy of injected electrons?

- Reliability depends on the energy of injected carriers

- Many tunneling components with different energy characteristics

Kamakura, JAP, 88(10), 2000.

#### Quantum yield by carrier separation

### $QY = \frac{I_{S/D}}{I_G}$

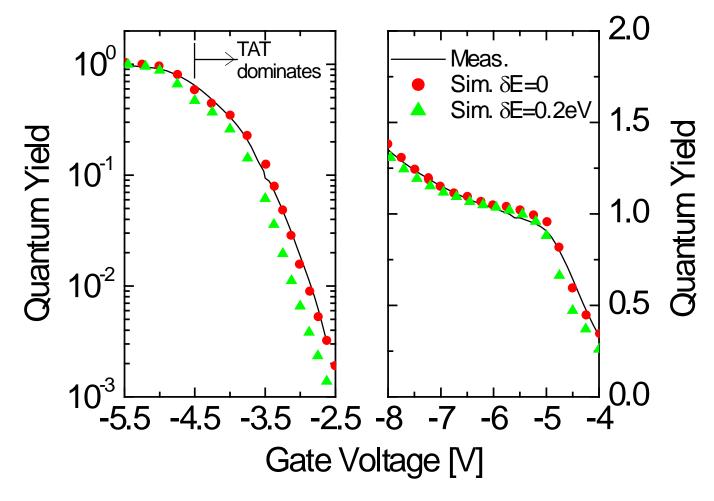

#### QY in unstressed Devices

#### QY in Stressed Devices

Ref. Koabashi, Analytical formulation of QY.

Alam ECE-695 25

#### Inelastic energy spectroscopy by QY

Apparently there is a structural relaxation for oxide defects ...

### Correlated SILC and QY ...

#### **Conclusions**

- Bulk traps require new measurement techniques such as pulse CV, SILC, and Quantum yield experiments.

- 2. Classical SILC probe mid-thickness taps (in thick oxides); LV-SILC appropriate probes surface states, in thin oxides).

- 3. Quantum Yield experiments show that native traps are elastic, while stress-induced traps are inelastic.

- 4. Low-frequency CP can be correlated to SILC and QY experiments for a comprehensive analysis.

#### References

#### Measurements theories are discussed in

- "SILC as a Measure of Trap Generation and Predictor of TBD in Ultrathin Oxides", M. A. Alam, IEEE Transaction on Electron Devices, 49 (2), pp. 226-231, 2002.

- The SILC characterization technique is discussed in detail by R. Degraeve et al., IRPS Proc. 2005.

"Degradation and Breakdown of 0.9 EOT gate dielectric". A similar paper is published in Microelectronics Reliability, 80, 440, 2005.

- LV-SILC is discussed by A. Ghetti, Proc. of IEDM, 22.3, 2000. "TBD Prediction from Measurement at Low field and Room temperature using a new Estimator".

- S. Takagi discusses inelastic defects by QY experiments in Proc. of IEDM, 13.2, 323, 1996 (Experimental Evidence of Inelastic Tunneling and a new I-V model for Stress induced leakage current)

- "Theory of Current-Ratio Method for Oxide Reliability: Proposal and Validation of a New Class of Two-Dimensional Breakdown-Spot Characterization Techniques," M. Alam, D. Monroe, B. Weir, and P. Silverman, Proceedings of International Electron Device Meeting, 2005.

- 2D BD-position also discussed in detail in "Exploratory analysis of the breakdown spots spatial distribution in metal gate/high-K/III–V stacks using functional summary statistics" by E. Miranda, E. O'Connor, P.K. Hurley. Microelectronics Reliability, 50, 1294, 2010.

#### **Review Questions**

- GI: Can you use charge pumping method to determine bulk trap density?

- G2: What method would you use if you want to determine defect close to the middle of the oxide?

- G3: Define Quantum yield. How does quantum yield change with electron energy?

- G4: Can you think of similar use of QY in HCI measurement? Explain.

- G5: QY experiments used gate injection technique. Can you use substrate injection?

- G6: There is a striking similarity between SILC and SRH in terms of the position of the traps. Can you say what the similarity is?

- G7: What is the difference between SILC and LV-SILC? Why do we use LV-SILC?