Course: Semiconductor Device Fundamentals

Level: Undergraduate

Module: B

Test: B3

Type: Closed Book, Closed Notes

**Note:** Available Info/Equation Sheets

Problem Weighting--- T2-1...40 (a,d-4; b,c,e,f-8) T2-2...28 (a,d-8; b,c,e-4) T2-3...32 (a,b-8; c,d,e,f-4)

|                           | T2 – 1<br>[Outcome–(iv)]                     | Score                           |

|---------------------------|----------------------------------------------|---------------------------------|

| Pictured below is the ene | ergy band diagram for a Si pn junction diode | maintained at room temperature. |

|                           |                                              | F                               |

| $E_{ m Fp}$               |                                              | $E_{\text{Fn}}$                 |

| FP                        |                                              | $E_1$                           |

|                           | •                                            |                                 |

|                           | . 0                                          |                                 |

- (a) What is the polarity and magnitude of the applied bias  $(V_A)$ ? [Record computational equation(s).]

- (b) Determine the built-in-voltage  $(V_{bi})$ . [Record computational equation(s).]

(c) Assuming a step-junction doping profile, determine W. [Record computational equation(s).]

- (d) Adding to the diagram in the problem statement, sketch and label the typically assumed positioning of the electron and hole quasi-Fermi levels ( $F_N$  and  $F_P$ ) through the depletion region.

- (e) What is the np product at x = 0?

(f) Adding carrier symbols ( $\bullet$ , O) to the diagram in the problem statement, identify (i) the major source of the diffusion current ( $I_{\text{DIFF}}$ ) and (ii) the source of the recombination—generation current ( $I_{\text{R-G}}$ ) flowing in the diode.

Score /28

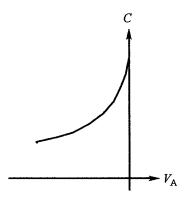

The reverse-bias capacitance  $(C-V_A)$  characteristic derived from a diode—it could be a p+-n step-junction diode or an n-type Schottky diode—is sketched below. It is further established that a least squares fit to the  $1/C^2$  versus  $V_A$  data yields

$$1/C^2 = \alpha_1 - \alpha_2 V_A$$

where  $\alpha_1$  and  $\alpha_2$  are positive constants.

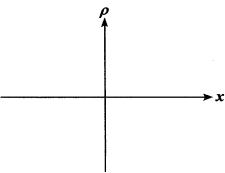

(a) Make a sketch of the **d.c.** charge density inside the diode during the C-V measurement. Specifically note the physical origin of the (+) and (-) charges on your sketch for both a p+-n step-junction diode and an n-type Schottky diode.

(b) Indicate how the term "quasistatically" relates to the capacitance measurement.

(e)  $V_{bi} = ?$  (An equation for  $V_{bi}$  is desired.)

|      | T2  | _ | 3   |      |

|------|-----|---|-----|------|

| [Out | tco | m | e–( | (v)] |

Score /32

Aluminum (Al) is the metal used in ECE557 to make external contacts to the backside of fabricated Si devices. Except for part (f), answer the following questions assuming the Al-Si contact is ideal and  $N_D = 8 \times 10^{16} / \text{cm}^3$  is the backside Si doping. T = 300 K,  $\Phi_M(\text{Al}) = 4.28 \text{eV}$ , and  $\chi(\text{Si}) = 4.03 \text{eV}$ .

(a) Determine  $\Phi_S$ , the Si workfunction.

(b) Roughly to scale, sketch the energy band diagram for the Al-Si contact under equilibrium conditions. Label relevant energy levels.

(c) Is the contact ideally ohmic or rectifying? Explain how you arrived at your answer.

(d)  $\Phi_B = ?$  [Record computational equation(s).]

(e)  $V_{bi} = ?$  [Record computational equation(s).]

(f) The Al-Si contact described in this problem is not really optimum for contacting the backside of fabricated Si devices. Indicate what must be done to achieve a low-resistance Al-Si contact.