### Well-Posed Device Models for Electrical Circuit Simulation

#### A Guide to Creating Robust Device Models

A. Gokcen Mahmutoglu, Tianshi Wang, Archit Gupta and Jaijeet Roychowdhury

March 25, 2017

#### **Synopsis**

This document provides guidelines for creating computational device models that work well in simulation. We build our discussion around the mathematical notion of "well-posedness". We show that the requirements for a model to be well-posed stem from the internal working mechanisms of simulators. Therefore, our main aim is to provide insight into the numerical procedures used by simulators in order to help model developers avoid ill-posedness issues. We start our discussion with an example that shows how an ill-posed Verilog-A model can produce different simulation results in different simulators. We then provide a step-by-step simulation case study. In this case study, we illustrate the role of device models in simulations by examining the steps a simulator goes through, from taking a netlist as input to producing a simulation result as output. Finally, we distill our discussion in a functional definition of a well-posed model. As an extension to our theoretical discussion, we also provide practical guidelines that should be followed by Verilog-A models in order to avoid ill-posedness issues.

This document is published as a part of the Nano-Engineered Electronic Device Simulation (NEEDS) initiative. NEEDS is an NSF-funded initiative whose charter includes the development of tools and techniques for the production of high-quality device models<sup>1</sup>:

"NEEDS has a vision for a new era of electronics that couples the power of billion-transistor CMOS technology with the new capabilities of emerging nano-devices and a charter to create high-quality models and a complete development environment that enables a community of compact model developers.

NEEDS Team: Purdue, MIT, UC Berkeley, and Stanford."

<sup>&</sup>lt;sup>1</sup>For more information about NEEDS please visit https://nanohub.org/groups/needs/.

#### 1 Introduction

Circuit designers rely on accurate simulators and simulators rely on accurate device models. For a device model, being accurate means featuring the right physical characteristics, *i.e.*, consisting of equations that capture every relevant physical effect. However, it also means offering an accurate and *robust numerical representation* of the physical device inside the simulator. Broadly speaking, we call device models *well-posed* if they are numerically robust representations of actual physical devices. In this document we unpack the concept of well-posedness with the aim of helping model developers to create device models that work well in various types of simulations and analyses.

Just like device models mimic physical objects, the simulator mimics the rules of physics. However simulators use numerical algorithms to perform this task and, therefore, they are subject to numerical limitations that are absent from the actual physical world. This in turn imposes limitations on the numerical techniques that can be used by device models. This ultimately means that simply putting the correct physical equations together is not enough to create a good device model. In this document, we explain what these limitations are and why they are important by providing insight into their origins.

Most ill-posedness problems in device models can be avoided by having a better understanding of different aspects of the role of a device model in simulation. In the subsequent sections we examine device models from three different perspectives.

- i. Mathematical: We show that in the core of every device model there is a system of Differential Algebraic Equations (DAEs).

- ii. Numerical: We demonstrate how the model DAEs are used in numerical simulations and analyses.

- iii. Practical: We give examples of device code which cause ill-posedness issues and provide recommendations on how to avoid them.

The structure of the rest of this document is as follows. In Section 2 we start with a short introduction to the Verilog-A behavioral modeling language and also introduce software tools, the Berkeley Model and Algorithm Prototyping Platform (MAPP) and the Berkeley Verilog-A Parser and Processor (VAPP), which we will use throughout this document. Section 3 introduces the concept of an ill-posed model without delving into numerical issues. We demonstrate how the most fundamental feature of the Verilog-A language (the contribution operator) can be used in a way that produces an ambiguous, ill-posed device model. In Section 4, we take the first step towards understanding what device models do inside simulators by demonstrating how a simple single transistor circuit is converted into a set of DAEs before any kind of numerical treatment is performed by the simulator. This conversion process and the subsequent numerical methods used by the simulator are key to understanding the necessary qualities for a model to be well-posed. We give a functional definition of well-posedness in Section 5 by listing the properties of a well-posed model. Section 6 offers a comprehensive guide on how to use Verilog-A to create models that are well-posed and compliant with the requirements of the NEEDS initiative.

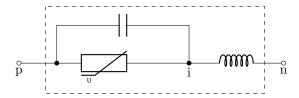

Fig. 1: A nonlinear resistor with a parallel capacitor and a series inductor.

#### 2 Practical Device Modeling with Verilog-A and MAPP

In this section, we provide a short review of some practical aspects of device modeling using Verilog-A and introduce software tools for model developers that were developed within the framework of the NEEDS initiative: MAPP and VAPP.

#### 2.1 The Verilog-A Modeling Language

Verilog-A is a domain specific, behavioral modeling language which has been adopted by the device modeling community as the default tool for developing and distributing compact device models. Detailed guides and tutorials for Verilog-A are readily available [1–3]. Here we will provide only a short introduction into the Verilog-A syntax and constructs that are essential for the rest of this document<sup>2</sup>.

**Listing 1:** Verilog-A model code for the circuit shown in Figure 1.

```

`include "disciplines.vams" // disciplines, electrical etc.

module nlresistor(p, n);  // model name and terminals

electrical p, i, n;

// nodes (internal ones too)

branch (p,i) br_res;

// call p->i branch br_res

// call i->n branch br_ind

branch (i,n) br_ind;

// define circuit parameters

parameter real R0 = 1e3 from [0:inf); // resistance

parameter real C = 1.0e-12 from (0:inf); // capacitance

parameter real L = 1.0e-15 from (0:inf); // inductance

10

11

12

analog function real nlfunc; // nonlinearity function

13

input v_in, G;

// define input variables

14

// define output variable

output i_out;

15

real v_in, i_out, G;

16

17

begin

_out = G*pow(v_in,3); // function core

18

19

end

20

endfunction

2.1

```

<sup>&</sup>lt;sup>2</sup> For further information on Verilog-A, the interested reader is referred to the relevant literature [1, 4].

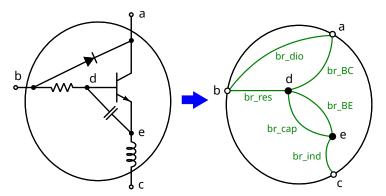

The example device model in Listing 1 is provided to illustrate the core concepts of Verilog-A. This piece of code represents a nonlinear resistor with an ideal capacitor connected to it in parallel and with an ideal inductor in series (shown in Figure 1). Lines 3 through 6 in Listing 1 define the model topology (terminals and internal nodes). The user defined function in lines 13–21 prescribes the nonlinear behavior of the device, and the model core in lines 23–27 associates this behavior with the previously defined model topology using the Verilog-A's contribution operator (<+).

The widespread adoption of Verilog-A by the circuit simulation community is not a coincidence. Verilog-A provides developers of circuit simulators with a way of importing device models that were not specifically developed for that simulator. This, in turn, enabled circuit designers and other end users of simulation software to share and use the same device models across different environments. At the end, the widespread adoption of Verilog-A has worked for the benefit of developers and end users of simulation software. However, the same cannot be said about the developers of the device models themselves. Although Verilog-A offers advantages to model developers for the distribution of new device model code, it still has no bearing on the actual model development cycle. This is because the use of Verilog-A requires an external simulator in which the developer imports and runs the model code. Employing such a method during the device model development phase is not practical because commercial simulators

- will run the model code only in a circuit and not in a stand-alone way,

- do not provide access to their numerical code, and

- do not offer programming tools such as a debugger.

For these reasons, many researchers in device modeling choose to develop their models in a programming environment like MATLAB<sup>®</sup>. The Berkeley Model and Algorithm Prototyping Platform (MAPP), developed within the framework of the NEEDS initiative, picks up on this predilection and offers a model development platform in MATLAB<sup>®</sup>, complete with a circuit simulator as well as access to various simulation algorithms and executable model code [5]. MAPP is accompanied by the Berkeley VAPP which is a separate software tool to import Verilog-A models into MAPP. Both MAPP and VAPP are freely available under GPL<sup>3</sup>. We offer a brief introduction into these tools in Section 2.2.

#### 2.2 MAPP — The Berkeley Model and Algorithm Prototyping Platform

MAPP is a software tool entirely written in MATLAB® that is specifically targeted for the development of device models and simulation algorithms [5]. MAPP uses a simple yet powerful

<sup>&</sup>lt;sup>3</sup>MAPP and VAPP both can be downloaded from Github at https://github.com/jaijeet.

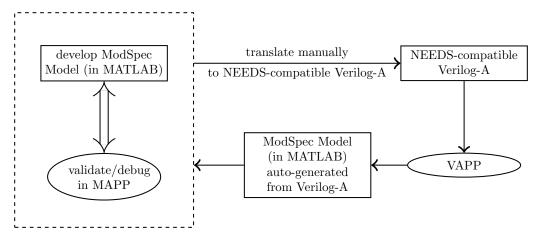

Fig. 2: Model development flow using MAPP and VAPP.

device model format called ModSpec [6]. Using ModSpec, instances of device models can be created (as MATLAB® data structures), added to circuits and simulated. It is also possible to use the model instance alone to perform simple analyses such as computing characteristic curves. Figure 2 depicts the steps in a typical model development flow using MAPP and VAPP. The development of a new device model starts at the upper left corner of the diagram and follows the steps indicated by the arrows.

Listing 2: Nonlinear resistor model with series capacitor implemented in ModSpec.

```

1 function MOD = nlresistor()

MOD = ee_model();

MOD = add_to_ee_model (MOD, 'modelname', 'nlresistor');

3

MOD = add_to_ee_model (MOD, 'terminals', {'p', 'n'});

5

MOD = add_to_ee_model (MOD, 'explicit_outs', {'ipn'});

6

MOD = add_to_ee_model (MOD, 'internal_unks', {'vin', 'iin'});

MOD = add_to_ee_model (MOD,

'parms', {'parm_C', 1e-12,...

8

parm_L', 1e-6,...

9

'parm_R0', 1000});

10

MOD = add_to_ee_model (MOD, 'fqei_all', @fqei_all);

11

MOD = finish_ee_model(MOD);

12

end

13

14 function [fe, ge, fi, gi] = fgei_all(S)

15

vbr_ind = S.vin;

16

ibr_ind = S.iin;

17

vpi = S.vpn - S.vin;

vbr_res = vpi;

18

19

fe(1,1) = nlfunc(vbr_res, 1/S.parm_R0);

20

fi(2,1) = -nlfunc(vbr_res, 1/s.parm_R0);

21

qe(1,1) = S.parm_C*vbr_res;

22

qi(2,1) = (-S.parm_C*vbr_res);

23

qi(1,1) = S.parm_L*ibr_ind;

fi(1,1) = (-vbr_ind);

```

```

25     fi(2,1) = fi(2,1) + ibr_ind;

26 end

27

28 function i_out = nlfunc(v_in, G)

29     i_out = G*v_in^3;

30 end

```

The first step in Figure 2 is to implement the device equations in MATLAB® and validate them via benchmarks and tests using the exploration and simulation infrastructure provided by MAPP. For instance, the nonlinear resistor model given in Listing 1 can be implemented in ModSpec as in Listing 2. The model properties are defined in the function nlresistor whose output is a model object. This object has fields such as modelname, terminals etc. that are defined in lines 3 through 7 in Listing 2. Lines 16–29 implement the model behavior and the auxiliary function, nlfunc, at the end defines the nonlinear behavior of the resistor just like in the Verilog-A model. As opposed to its Verilog-A counterpart, this ModSpec model can immediately be instantiated with

```

MOD = nlresistor();

```

The model instance can be called directly by providing values for the input variables (vpn, vin and iin) in order to examine its outputs, e.g.,:

```

vpn = 2;

vpi = 1;

iin = 1e-5;

out = MOD.fi(vpn,[vpi;iin],{},{},MOD);

```

or it can be included in a circuit object by first creating the circuit

```

ckt.cktname = 'nlres_test_circuit';

ckt.nodenames = {'p'};

ckt.groundnodename = 'gnd';

```

and then adding the model object to this circuit

```

ckt = add_element(ckt, nlres, 'R', {'p', 'gnd'}, {}, {});

```

Listing 3: Transient simulation of the nonlinear resistor model in MAPP.

```

1 ckt.cktname = 'nlres_test_circuit';

2 ckt.nodenames = {'p'};

3 ckt.groundnodename = 'gnd';

4

5 vM = vsrcModSpec();

6 nlres = nlresistor();

7

8 tranfuncargs.f0 = 1e6;

9 tranfuncargs.A = 3;

10 tranfunc = @(t, args) (args.A*sin(2*pi*args.f0*t));

11

12 ckt = add_element(ckt, vM, 'vsrcl', {'p', 'gnd'}, {},...

```

```

13

{{ 'tran', tranfunc, tranfuncargs}});

14 ckt = add_element(ckt, nlres, 'R', {'p', 'gnd'}, {}, {});

15 \ \text{ckt} = \text{add\_output(ckt, 'p');} \ \% \ \text{node voltage of 'p'}

16 ckt = add_output(ckt, 'i(vsrc1)', 100);

17 DAE = MNA_EqnEngine(ckt);

18

19 % DC analysis

20 dcop = dot_op(DAE);

21 feval(dcop.print, dcop);

23 % run transient simulation

24 xinit = feval(dcop.getsolution, dcop);

25 T0 = 1/\text{tranfuncargs.f0}; tstart = 0; tstep = T0/100; tstop = 2*T0;

26 TRobj = dot_transient(DAE, xinit, tstart, tstep, tstop);

28 % plot DAE outputs (defined using add_output inside vsrcRCL_ckt.m)

29 feval(TRobj.plot, TRobj);

```

We can then add outputs to the circuit, create an equation system out of it and perform, for example, a transient simulation. The entire code for this flow is provided in Listing 3. The important parts of the script occur in the following lines:

**1–3:** create the circuit object,

**5–6:** create a voltage source and the nonlinear resistor,

**8–16:** define circuit element properties and the circuit topology,

17: create differential algebraic equation (DAE) object using the circuit,

19-16: run initial DC and transient simulations,

**29:** display the result.

Device models should be tested with a multitude of simulation settings. They should be subjected to various types of simulations/analyses with various test inputs. After making sure that our model performs well in different types of tests, we would continue with the steps in Figure 2. To deploy our model, we would create its Verilog-A version. In order to make sure that our Verilog-A code produces the same output as the original model, we can translate the Verilog-A code back into ModSpec using VAPP. VAPP is still under heavy development but it already can produce simulation ready ModSpec models via its simple user interface. Model translation using VAPP can be as simple as making the following function call

```

va2modspec('nlresistor.va');

```

VAPP can also be used for importing existing Verilog-A models into MAPP for testing and development purposes or for building prototypes of small experimental circuits and simulating them.

As mentioned above, both MAPP and VAPP are freely available under GPL. Users are encouraged to get involved with the development by filing bug reports and contributing to the code base. We recommend that readers download and install MAPP and VAPP in order to be able to run the provided pieces of test code while going through this document.

# 3 A Verilog-A Model with Inconsistent Behaviors in Different Simulators

In this section we go through a case study using a Verilog-A device model that produces different results in two different simulators, Spectre and HSPICE. This case study shows that it is relatively easy to create an ill-posed model in Verilog-A. The example model we use is a simple two terminal device which does not have any complicated numerical components. We simply combine two basic features of Verilog-A to create a model which can be interpreted in more than one way. This causes the model output to be *not uniquely defined* and therefore the model to be ill-posed.

Listing 4: An ill-posed two terminal Verilog-A model.

When the DC operating point of the model in Listing 4 is computed with Spectre, the answer is  $\mathbb{I}(p,n) = 1\mathbb{A}$ . However, when the same analysis is performed with HSPICE, we obtain a different answer:  $\mathbb{I}(p,n) = 0.5\mathbb{A}$ . In the remainder of this section we explain why this is the case.

The main feature of the Verilog-A modeling language is the *contribution operator* (<+). In Verilog-A, the physical structure of a model is given by defining *nodes* and *branches* and the contribution operator enables us to assign (contribute) a voltage or current to a branch. For example, a resistor is defined as follows.

Listing 5: Resistor model in Verilog-A.

In Listing 5 (line 6) a current value is computed (V(p,n)/1e3) and then this value is added (contributed) using the contribution operator to the current between the p and n nodes. This is a very intuitive way of defining models. However, a programming language has to be logically precise and in this case, intuition might not always be helpful.

A prominent example of a language feature being extended beyond its immediate meaning is the notion of an *implicit contribution* in Verilog-A. Consider the model given in Listing 6.

Listing 6: Implicit diode model from the Verilog-AMS Language Reference Manual [7].

```

module implicit_diode (p, n);

inout p, n;

electrical p, n;

parameter real IS = 1e-12 from (0:inf);

parameter real R = 1 from (0:inf);

analog begin

I(p,n) <+ IS*(limexp((V(p,n) - R*I(p,n))/$vt) - 1);

end

endmodule</pre>

```

This model describes a simple diode and it was directly taken from the Verilog-AMS Language Reference Manual [7, Section 5.6.6]. The expression in line 7 defines the current  $\mathbb{I}(p,n)$  by placing it on the left-hand side (LHS) of the contribution operator. However, the same current value ( $\mathbb{I}(p,n)$ ) appears on the right-hand side (RHS) of the contribution as well. What does that mean? Obviously, we cannot compute the RHS of the expression first and add it to  $\mathbb{I}(p,n)$  because the RHS depends on the value of  $\mathbb{I}(p,n)$ . The intuitive notion of a contribution does not apply here.

Statements like the one in Listing 6, line 7 are called *implicit contributions*. This means that the simulator interpreting the model has to bring both sides of the contribution statement together and solve it by setting the whole expression equal to zero. For the model in Listing 6:

```

I(p,n) - IS*(limexp((V(p,n) - R*I(p,n))/$vt) - 1) = 0

```

The Verilog-A language allows this usage simply because it is syntactically possible. However, the behavior of models with implicit contributions vary across simulators. In what follows, we will examine the behavior of a simple model with an implicit contribution in HSPICE and Spectre<sup>4</sup>.

The model we will experiment with is similar to the one given in Listing 6 but, for simplicity, we replace the diode equation with a simpler equation. This new model is given in Listing 7

Listing 7: Simplified implicit model.

<sup>&</sup>lt;sup>4</sup>HSPICE and Spectre version used are as follows. HSPICE: Version H-2013.03 64-BIT. Spectre: Version 7.2.0 64bit.

The contribution in line 6 in Listing 7 forces the model to compute an I(p, n) value that satisfies the polynomial equation

$$x^2 - 2x + 1 = 0. (1)$$

Hence, we expect that if we simply connect this device to a voltage source and compute the operating point (DC analysis), we should obtain

$$I(p,n) = 1.$$

This should be the case independent of the value of the voltage source.

When simulated with Spectre, we obtain

$$I(p,n) = 998.047m$$

.

By tightening the value of reltol to 1e-9 we get the expected answer

$$I(p,n) = 1A.$$

However, if the same circuit is simulated with HSPICE, we receive a different answer.

$$I(p,n) = 493.8272m$$

In fact, when a sweep is performed, HSPICE seems to generate different results for different voltage source values.

| volt.    | current.            |

|----------|---------------------|

| VOIC     |                     |

|          | VS                  |

| 0.       | -518.5185m          |

| 1.00000  | -386.8313m          |

| 2.00000  | -401.4632m          |

| 3.00000  | -399.8374m          |

| 4.00000  | -400.0181m          |

| 5.00000  | -399 <b>.</b> 9980m |

| 6.00000  | -400.0002m          |

| 7.00000  | -400.0000m          |

| 8.00000  | -400.0000m          |

| 9.00000  | -400.0000m          |

| 10.00000 | -400.0000m          |

With a small modification to the example model in Listing 7, we obtain the model given in the beginning of this section. The model given in Listing 4 is reproduced below in Listing 8 for convenience.

Listing 8: Modified simplified implicit model.

```

include "disciplines.vams"

module implicit_model (p, n);

inout p, n;

electrical p, n;

analog begin

I(p,n) <+ 0.5*I(p,n)*I(p,n);</pre>

```

Note that this model is similar to the simplified implicit model in Listing 7 except that the implicit contribution in line 6 does not contain the additive constant 0.5. Instead, the model contains a separate contribution to  $\mathbb{I}(p,n)$  in line 7 with the value of the missing constant in the implicit contribution. This contribution adds a constant value to  $\mathbb{I}(p,n)$ . If  $\mathbb{I}(p,n)$  was an explicitly defined current, we would interpret this extra contribution as "add 0.5 to the value of  $\mathbb{I}(p,n)$ ". However, in this case  $\mathbb{I}(p,n)$  does not have an explicit value. So, how should the simulator interpret line 7 in Listing 8? One way to interpret this is to construe the second contribution as an addition to the implicit equation and solve exactly the same equation given in (1). This is indeed how Spectre interprets it. However, HSPICE seems to do something different. It ignores the implicit contribution altogether and produces

$$I(p,n) = 500.0000m.$$

This simple example shows that even syntactically correct, expressions in Verilog-A might not always be meaningful or they can be interpreted differently by different simulators. The only resolution for this problem is to restrict valid Verilog-A code to a subset of its current form. This subset must be able to support all the features a well-posed compact model might require. However, it also should exclude any expressions that might cause the model to be *ill-posed*. To do this, we will need to answer the following question: *what task does a computational model perform inside a simulator?* We answer this question with a step-by-step example in Section 4.

#### 4 The Role of Compact Models in Simulation — a Case Study

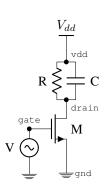

Fig. 3: CS amplifier.

In this section, the simple circuit in Figure 3 will be used to illustrate basic concepts about compact device models and their role in circuit simulation. Replicating the procedure followed by a simulator, we will start with a network of devices and arrive at a set of DAEs that describe the circuit dynamics. Our aim is to make clear how device models are used by a circuit simulator.

Figure 3 depicts a common source amplifier with four circuit elements: a voltage source (V), a MOSFET (M), a capacitor (C) and a resistor (R). A circuit is described to the simulator in terms of *nodes*, *branches* and *devices*. Listing 9 shows how this is done for the circuit in Figure 3. A text file similar to the one in Listing 9, defining the devices in the circuit and their connections, *i.e.*, the circuit topology, is traditionally called a *netlist*.

Lines 1–3 in Listing 9 set the name of the circuit and the names of its nodes. lines 5–9 create *instances* of devices. One of these devices, the voltage source, is added between the nodes vdd and gnd in lines 11–16

and its DC voltage is specified to be 1 volt (line 16). Lines 18–20 add the transistor to the circuit.

The second voltage source in the circuit is added in lines 22–28 while the final lines, 30–31, add the parallel resistor and capacitor pair.

Listing 9: A netlist for the circuit in Figure 3 (executable in MAPP).

```

1

cktnetlist.cktname = 'cs amp';

cktnetlist.nodenames = {'vdd', 'drain', 'gate'};

2

3

cktnetlist.groundnodename = 'gnd';

4

5

MOSFET = SH_MOS_ModSpec();

6

VS_VDD = vsrcModSpec();

7

VS_IN = vsrcModSpec();

8

RES = resModSpec();

9

CAP = capModSpec();

10

11

12

cktnetlist = add_element(cktnetlist, VS_VDD, ...

13

'Vdd',...

14

{'vdd', 'gnd'},...

15

{},...

16

{{'E', {'DC', vdd}}});

17

18

cktnetlist = add_element(cktnetlist, MOSFET,...

19

'NMOS',...

20

{'drain', 'gate', 'gnd'});

21

22

vinoft = @(t, args) args.A*sin(2*pi*args.f*t);

23

vinargs.A = 1; vinargs.f = 1;

24

cktnetlist = add_element(cktnetlist, VS_IN, ...

25

'Vin',...

{'gate', 'gnd'},...

26

27

{},...

28

{{ 'tr', vinoft, vinargs}});

29

30

cktnetlist = add_element(cktnetlist, RES, 'R', {'vdd', 'drain'}, 1e5);

cktnetlist = add_element(cktnetlist, CAP, 'C', {'vdd', 'drain'}, 1e-12);

31

```

The definition of a simple linear resistor in MAPP is given in Listing 10. When called with a voltage value as input, the function in lines 15–17 will query the resistance value of that specific resistor instance and return the current flowing through the device. When we talk about device models in simulators, what we primarily refer to is this input-output relationship function.

**Listing 10:** Model code for a resistor in MAPP. The function for the voltage-current characteristic of the resistor is given as £ (S) in lines 15–17.

```

9

MOD = add_to_ee_model(MOD, 'parms', {'R', 1e3});

10

% define the input-output function (given below)

11

MOD = add_to_ee_model(MOD, 'f', @f);

12

MOD = finish_ee_model(MOD);

13

end

14

15

function ipn = f(S) % vpn and R are defined through S

16

ipn = S.vpn/S.R;

17

end

```

Device code can be considerably more complex (thousands of lines) for devices like transistors. In general, a device has also more than one output. For instance, an ideal capacitor might look like the code given in Listing 11. This function tells the simulator that when there is a voltage vpn across the terminals of the capacitor, a charge of magnitude q accumulates at each of those terminals while there is no direct current flow (f=0) through them (the charge component can, of course, lead to its own current).

Listing 11: Model code for a capacitor in MAPP. Note the definition of the fq function in line 10 instead of only f.

```

function MOD = capModSpec()

2

MOD = ee_model();

3

MOD = add_to_ee_model(MOD, 'terminals', {'p', 'n'});

MOD = add_to_ee_model(MOD, 'explicit_outs', {'ipn'});

4

MOD = add_to_ee_model(MOD, 'parms', {'C', 1e-12});

5

MOD = add_to_ee_model(MOD, 'q', @fq);

7

MOD = finish_ee_model(MOD);

8

end

10

function [f, q] = fq(S)

11

f = 0;

q = S.C*S.vpn;

12

13

end

```

For devices with more than two terminals, the output variables of the device function will be vector valued. This is illustrated in Listing 12 for the Shichman-Hodges transistor model [8].

**Listing 12:** Shichman-Hodges transistor model. Note that the output is a  $2 \times 1$  vector.

```

1

function MOD = SH_MOS_ModSpec()

2

MOD = ee_model();

MOD = add_to_ee_model(MOD, 'terminals', {'d', 'g', 's'});

3

MOD = add_to_ee_model(MOD, 'explicit_outs', {'igs', 'ids'});

MOD = add_to_ee_model(MOD, 'parms', {'Beta', 1e-3, 'vth', 0.5});

MOD = add_to_ee_model(MOD, 'f', @f);

5

6

7

MOD = finish_ee_model(MOD);

8

end

10

function iout = f(S)

11

igs = 0;

12

if S.vgs < S.vth

13

ids = 0; % cutoff region

```

```

14

if S.vds - S.vgs > -S.vth

15

17

ids = 0.5 * S.Beta * (S.vgs - S.vth)^2;

18

19

20

ids = S.Beta * S.vds * (S.vqs - S.vth - 0.5*S.vds);

21

22

end

23

iout = [iqs; ids];

24

end

```

Using the information about the circuit topology, the device equations are put together to obtain a larger set of equations describing the whole circuit. There is more than one way of generating circuit equations. However, all of them rely on the same principles: combine *constitutive equations* with *conservation equations*. In our case, the constitutive equations will be obtained by invoking device functions and the conservation equations will be built via Kirchhoff's Current Law (KCL) and Kirchhoff's Voltage Law (KVL).

The network in Figure 3 has three non-ground nodes (vdd, drain and gate). Two of these nodes, vdd and gate, have fixed voltages because they have voltage sources attached to them. In the end, we are left with only one node that has an unknown voltage: the drain of the transistor. The systematic form of this analysis, where the number and the type of unknowns are determined, is called the *nodal analysis*.

Since there is only one unknown in the circuit (the drain voltage,  $v_{drain}(t)$ ), the size of the equation system will be one. In order to create this single equation, the simulator will go through the devices in the circuit. It will calculate the outputs of their device functions and combine them using KCL, with appropriate signs as follows:

$$-\underbrace{\frac{\left(v_{dd} - v_{drain}(t)\right)}{R}}_{\text{RES.f}\left(v_{dd} - v_{drain}(t)\right)} - \underbrace{\frac{d}{dt}}_{\text{CAP.q}\left(v_{dd} - v_{drain}(t)\right)} + \underbrace{I_{ds}\left(v_{drain}(t), v_{gate}\right)}_{\text{MOSFET.}f\left(v_{drain}(t), v_{gate}\right)} = 0 \tag{2}$$

In equation (2), the term under the time differentiation operator is a function of the independent variable,  $v_{drain}(t)$ . An alternative way of writing this equation is to represent the charges in the circuit as independent variables which are defined by algebraic equations.

$$\frac{\mathrm{d}Q(t)}{\mathrm{d}t} = -\frac{(v_{dd} - v_{drain}(t))}{R} + I_{ds}(v_{drain}(t), v_{gate})$$

$$Q(t) = v_{dd} - v_{drain}(t)$$

(3)

Notice how the set of equations in (3) contains one differential and one algebraic equation. This is why circuit equations are generally called Differential Algebraic Equations (DAEs).

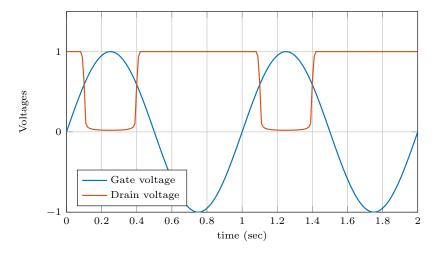

The circuit in Figure 3 can be simulated in MAPP by first running the script given in Listing 9 to construct the circuit, and then calling the code in Listing 13 to run a transient simulation. The result of this simulation is shown in Figure 4.

Fig. 4: The result of the transient simulation in Listing 13.

Listing 13: Transient simulation and plotting code for the netlist in Listing 9 (executable in MAPP).

```

DAE = MNA_EqnEngine(cktnetlist);

1

2

3

xinit = zeros(feval(DAE.nunks, DAE), 1);

4

xinit([1,2]) = vdd;

5

tstart = 0; tstep = 1e-2; tstop = 2;

6

LMSobj = transient(DAE, xinit, tstart, tstep, tstop);

8

% plot selected state outputs

souts = StateOutputs(DAE);

9

10

souts = souts.DeleteAll(souts);

souts = souts.Add({'e_gate', 'e_drain'}, souts);

11

feval(LMSobj.plot, LMSobj, souts);

```

In going through the case study above, our aim was to clarify the role of compact models in simulations. In summary, the simulator evaluates the device function for each compact model and combines their outputs using KCL and KVL in order to construct a set of DAEs for the whole circuit. This DAE system is then either numerically integrated as in the case of transient simulation<sup>5</sup> or used in other numerical algorithms such as shooting and harmonic balance. Therefore, for a successful simulation, the simulator needs to be able to construct a DAE system that is both well-defined and sufficiently well-behaved for the subsequent numerical analysis. Since the DAE system is composed of its smaller constituents, *i.e.*, the device models, this requirement can only be satisfied if every device model in the circuit is well-posed.

<sup>&</sup>lt;sup>5</sup>This procedure is further described in Appendix A.

#### 5 Well-Posedness

The mathematical notion of well-posedness applies to problems posed in form of differential equations and partial differential equations [9]. A mathematical problem is said to be well-posed if

- a solution to the problem exists,

- the solution to the problem is unique,

- the solution varies smoothly with respect to the parameters in the problem.

We borrow this notion and associate it with device models. We call device models well-posed if they produce well-posed circuit DAEs. Well-posedness imposes restrictions on device models from both a numerical and a programming standpoint. In this section, we discuss the key properties of a well-posed model.

We start by showing how a single device model itself can be expressed in a DAE formulation. As we have seen in equation (2), the simulator constructs the circuit DAEs by receiving the differential and algebraic parts of model equations from each device in the circuit. The most general form of model equations can be written as follows [5].

$$\frac{\mathrm{d}}{\mathrm{d}t}\vec{q}_{e}(\vec{x}(t), \vec{y}(t), \vec{u}(t)) + \vec{f}_{e}(\vec{x}(t), \vec{y}(t), \vec{u}(t)) = \vec{z}(t)

\frac{\mathrm{d}}{\mathrm{d}t}\vec{q}_{i}(\vec{x}(t), \vec{y}(t), \vec{u}(t)) + \vec{f}_{i}(\vec{x}(t), \vec{y}(t), \vec{u}(t)) = \vec{0}$$

(4)

Where  $\vec{x}(t)$  contains the terminal inputs and  $\vec{z}(t)$  the terminal outputs of the device. The internal unknowns of the device are represented by  $\vec{y}(t)$ , and  $\vec{u}(t)$  contains the time varying inputs to the device such as independent voltage and current sources. The four functions  $\vec{q}_e$ ,  $\vec{f}_e$ ,  $\vec{q}_i$ ,  $\vec{f}_i$  characterize the dynamical behavior of the device. The functions  $\vec{q}_e$  and  $\vec{q}_i$  represent the differential part of the device equations and  $\vec{f}_e$  and  $\vec{f}_i$  the algebraic ones.<sup>6</sup>. ModSpec uses this structure to define device models. We have been explicitly prescribing the  $\vec{f}$  and  $\vec{q}$  functions of the ModSpec models we have seen so far (e.g., lines 19-25 in Listing 2). The DAE system in equation (4) has to be clearly and uniquely defined for every device model and this condition lies in the heart of creating well-posed models.

The restrictions for device models to be well-posed stem from multiple sources. The most important of these is the fact that simulators work in an iterative manner. At each step, the simulator checks how far away it is from satisfying the system equations by evaluating a residual function<sup>7</sup>. Then it computes its next guess by taking a step in the direction of decreasing error. This process is known as the *Newton-Raphson (NR) algorithm* and it requires the residual function to be well-defined for a wide range of input values as well as to be continuous and smooth. Because the residual function is computed hierarchically using individual device models, these conditions apply to device models as well. Well-posedness requirements that stem from this numerical procedure are as follows.

<sup>&</sup>lt;sup>6</sup>For a detailed explanation of this equation system please see [5] and [6].

<sup>&</sup>lt;sup>7</sup>Please see Appendix A for a brief explanation of how this is done.

- 1. Finite and unique outputs: The device functions  $(\vec{q}_e, \vec{f}_e, \vec{q}_i, \vec{f}_i)$  must have mathematically valid outputs for any mathematically valid input. In particular, this output should be unique and finite. Functions like  $\frac{1}{a-x}$  become unbounded for x=a. Other functions are not defined for certain values of x. For example when  $\sqrt{x}$  or  $\log(x)$  is used, one has to make sure that their arguments are positive.

- 2. Continuous and smooth outputs: When finding the zero of a function, the NR algorithm uses the derivative of that function in order to take a step in the direction of decreasing function value. For this reason, the  $\vec{q}_e$ ,  $\vec{f}_e$ ,  $\vec{q}_i$ ,  $\vec{f}_i$  functions of a device must be continuous, *i.e.*, they must not contain any sudden jumps. They must also be smooth at least up to first order, *i.e.*, their first order derivatives with respect to the terminal inputs,  $\vec{x}$ , and the internal unknowns,  $\vec{y}$ , must exists. Higher order derivatives are highly desirable and, in the ideal case, the device functions should be in  $C^{\infty}$ , *i.e.*, all orders of derivatives should exist [10].

- 3. Wide input range: Device model functions must produce real, finite outputs for a wide range of input and internal unknown values. The NR algorithm might probe devices with input values that are not physically possible under normal device operation. For example, a real transistor would burn if we applied a 1000 V potential across its drain and source terminals. However, the NR algorithm might very well call the device functions with a 1000 V input value while it is searching for a solution. Therefore, device models must be able to supply real and finite output values for a wide range of terminal voltages/currents and internal unknown values.

Apart from "low-level" numerical requirements, there are also "high-level" requirements for a model to be well-posed. These requirements are related to the model specification format in which the model is described. Today, most electrical device models are described using the Verilog-A behavioral modeling language. Although the Verilog-A language offers an intuitive model description framework with features such as its node/branch structure, time differentiation/integration operators, functionality for collapsing nodes etc., many of these features allow statements that are problematic from a well-posedness standpoint. Such problematic statements, when translated to a lower level, executable model description such as ModSpec, create either ambiguous or nonsensical models.

The most crucial high-level requirement for a model is that it has to *work in all analysis types*. Different analyses use the device functions in different ways. For example, transient simulation computes circuit variables at consequent time points, one at a time. AC analysis, on the other hand, linearizes the circuit around a DC operating point, performs computations using phasors and does not directly involve time. Therefore, it is erroneous to assume that when the device functions are called, it will always be at a well-defined time point.

The simple way of preventing high-level ill-posedness issues is to always formulate the device equations in form of equation (4). This, however, does not mean that it is sufficient to simply return some  $\vec{f}$  and  $\vec{q}$  functions for a device to be well-posed. In addition to formulating device equations in DAEs, one must adhere to the following rules.

1. The size of the DAE must stay constant during the entire simulation/analysis. Any statement that tries to change the size of the model equations during an analysis causes the model to

be ill-posed. A bias dependent node collapse is a typical example of this type of statement.

- 2. All device dynamics should be expressed using the DAE formulation. This means that no explicit time integration/differentiation may be performed inside the device code itself.

- 3. The device must communicate with the simulator only through device function calls. The device should be agnostic to the past, present or future state of the simulator. This means events such as crossing a voltage value or starting a certain type of analysis must not trigger any special event control routines in the device code.

- 4. Device code must not make any reference to absolute simulation time. It has to be able to run in analyses, such as AC and DC, where time is not directly involved.

- 5. The device DAEs must have a deterministic core that consistently returns the same outputs for the same inputs. All randomness information in the device (such as noise) must be implemented through special functions that tell the simulator what kind of randomness is to be added to the device equations, *e.g.*, white/flicker noise. There must not be any explicit pseudorandom number generation within the device code.

The rules in the above list are general guidelines that will ensure the correct operation of device models in every simulation/analysis type. The rather abstract nature of these rules will be more concretely explained in Section 6 where we discuss how to avoid ill-posedness issues in Verilog-A models.

#### 6 NEEDS Compatible Device Modeling Using Verilog-A

The chief *raison d'etre* for device models is that they should work properly in simulators; a large portion of their merit stems from how well they achieve this goal. In this section, we discuss best practices to be observed in implementing compact device models in Verilog-A. We propose best practices for developing device models that are well-posed and minimize the risk of running into problems during numerical simulations and analyses. The guidelines and rules laid out here are mandated by the NEEDS initiative; accordingly, device models that follow these guidelines will be called "NEEDS compatible".

In Sec. 6.1, we list recommended practices for developing device models in Verilog-A and rules for producing NEEDS compatible models. Section 6.2 provides an overview of the most important tests device models should be subjected to before they are considered robust enough for a public release. We also offer a five-step guide on general model development methodology using Verilog-A in Section 6.3.

#### **6.1 Verilog-A: Best Coding Practices**

In this section, we will provide a list of dos and don'ts for coding *simulation-ready* device models in Verilog-A. As mentioned earlier, models which follow the recommendations in this list will be deemed "NEEDS compatible". The NEEDS initiative stipulates that device models published on

the NEEDS website must be NEEDS compatible. An overview of the recommendations and rules for NEEDS compatibility is given in the list below; the rest of this section expands on these.

- 1. DO NOT use a global ground node.

- 2. DO use branches.

- 3. DO declare and initialize all variables and DO NOT use memory states.

- 4. DO NOT use event control statements.

- 5. DO NOT use analysis dependent functions.

- 6. DO use ddt, but only in allowed ways.

- 7. DO NOT use idt.

- 8. DO NOT use time-varying functions.

- 9. DO NOT use random number generators.

- 10. DO take great care when using implicit equations.

- 11. DO NOT allow any nodes in your model without having at least one branch with a well-defined contribution attached to it.

- 12. DO NOT use bias-dependent switch branch and node collapse conditions.

- 13. DO use parameter ranges.

Table 1: List of "do's and dont's" for producing NEEDS compatible Verilog-A models.

#### 1. DO NOT use a global ground node.

Example 1 shows part of a model which has an access function with only one node as argument (V(p) in line 5). This means that the model relies on a *global ground* (which represents a zero volt reference). This usage is not NEEDS compatible. To see why, consider the scenario where the potentials at every node of the device is increased by the same amount. Since in this case the potential differences across the device remain the same, we would expect no change in the outputs of the device. However this principle does not hold for the model in Example 1, because V(p) and hence I(p) would change.

<sup>&</sup>lt;sup>8</sup> If the device really needs a connection to the global ground, it should add an extra terminal which should be connected (at the circuit netlist level) to the global ground.

#### EXAMPLE 1 NOT NEEDS compatible 1 module exampleModel(p, n); electrical p, n; 3 branch (p,n) br\_res; 5 $I(br\_res) <+ G*V(p);$ 7 endmodule NEEDS compatible 8 module exampleModel(p, n); electrical p, n; 10 branch (p,n) br\_res; 11 12 I(br\_res) <+ G\*V(br\_res);</pre> 13 14 endmodule

One may still use probes/sources in Verilog-A with a single node argument while being physically correct, *e.g.*,

```

1    I(br_res) <+ G*(V(p) - V(n));

```

Even so, using probes/sources with single node arguments is not recommended, because it can easily lead to mistakes in more complicated expressions. Instead of using single node arguments in probes/sources, NEEDS recommends using branches as shown in Example 1, line 12 and discussed below in Rule 2.

#### 2. DO use branches.

Verilog-A supports access functions (V(), I(), Pwr() etc.) in the following equivalent forms:

```

NOT NEEDS compatible

1 V(node1) - V(node2)

Accepted by NEEDS but not recommended

2 V(node1, node2)

NEEDS compatible

3 branch (node1, node2) br_label;

4 V(br_label)

```

NEEDS compatibility requires that all probes and sources use branches. With this convention, the risk of running into problems such as the one discussed above in rule 1 will be eliminated.

#### 3. DO declare and initialize all variables and DO NOT use memory states.

```

EXAMPLE 3

NOT NEEDS compatible

1 //The calculation of charges:

3 \text{ aa=1+gamma/(2*sqrt((phib-Vbb+dvg)))};

4 qi=(2/3)*(1+x+pow(x,2))/(1+x);

5 Qinvq=Qinv*qi;

6 Vxint=V(Vx)+(tipe*dir)*dvg;

7 Vyint=V(Vy)-(tipe*dir)*dvg;

8

9 ...

10

11 //NVsat charge model: for long channel drift/diffusion

→ without saturated

drift velocity

12 x=(1-Fsatq);

den=15*pow((1+x),2);

13

qsc = (6+12*x+8*pow(x,2)+4*pow(x,3))/den;

14

15

qdc = (4+8*x+12*pow(x,2)+6*pow(x,3))/den;

16 //end of NVsat charge model

```

A common mistake in Verilog-A models is leaving the variables undeclared/uninitialized, *e.g.*, under the assumption that the compiler will create a new variable and initialize it

automatically to zero. This is a dangerous programming practice. Example 3 was taken from a real life model where an uninitialized variable was the source of a bug. Notice that the variable x is used (on line 4) before it is set (on line 12).

Uninitialized variables can also cause so-called "hidden states" or "memory states". For instance, a hidden state occurs if a variable is assigned a value during one evaluation of the device function and is accessed during consequent evaluations without being assigned a new value. This causes problems in analyses such as shooting [11].

Conditional statements (e.g., if/else) that are *bias-dependent* are usually the culprit for hidden states. Example 4 shows the relevant part of a model where this problem occurs<sup>9</sup>.

```

EXAMPLE 4

NOT NEEDS compatible

1    real i_out;

2    analog begin

3     if (V(in) < 1) i_out = 0;

4     if (V(in) > 2) i_out = 1;

5

6     I(out) <+ i_out;

7    end</pre>

```

In Example 4, the <code>i\_out</code> variable is declared but has no default value. In the model body, this variable gets a value assigned to it only when the input voltage value is outside the interval [1,2]. It is not prescribed what value <code>i\_out</code> is to assume when the input voltage satisfies <code>V(in) \in [1,2]</code>. The expectation in the model in Example 4 is that the simulator would retain the value of <code>i\_out</code> from one call of the device function to the other. NEEDS compatibility requires that, for any given input to the device function, the values of all variables in the model are uniquely defined without depending on previous input values. For this reason, the usage of hidden states is not NEEDS compatible  $^{10}$ .

#### 4. DO NOT use event control statements.

Event control statements in Verilog-A start with the '@ ()' delimiter and tell the simulator to perform tasks at certain points in the simulation. The code in Example 5 line 1, for instance, tells the simulator to set the value of register a to register at the positive edge of a clock cycle. Similarly, the model code in lines 2–4 performs a certain task when the input voltage crosses the 1 Volt threshold. Other possible event control statements in Verilog-A are listed in [7, Section 5.10].

<sup>&</sup>lt;sup>9</sup>Seen on designers-guide.org (http://www.designers-guide.org/Forum/YaBB.pl?num=1170146863). In this model, hidden states are used as a "technique" to create hysteresis-like behavior. For a proper way of implementing hysteresis in compact models see [12].

<sup>&</sup>lt;sup>10</sup> Moreover, discovering hidden states in larger models is a nontrivial task. Model developers are strongly advised to keep their models free of hidden states.

# NOT NEEDS compatible 1 @(posedge clk\_a) register\_a = register\_b; NOT NEEDS compatible 2 @(cross (V(in), +1)) begin 3 crossings = crossings + 1; 4 end

NEEDS compatibility forbids the use of event control statements for the simple reason that they do not make sense in every simulation and analysis performed by the simulator. For example there are no threshold crossings in DC analysis or clock edges in AC analysis. As explained in Section 4, models are used to construct DAEs. Whatever analysis the simulator performs is performed on this DAE system and the DAE system must stay the same independent of the type of analysis. This means models should not be aware of what type of analysis is performed.

#### 5. DO NOT use analysis dependent functions.

Analysis dependent functions in Verilog-A are used to make models behave differently in different analyses such as AC, DC, transient, *etc*. The model in example 6 uses the analysis() function to assign different values to the out variable in different types of analyses [13]. If the simulator computes a DC operating point or initial conditions, out gets the negative sign of the input voltage.

```

EXAMPLE 6

NOT NEEDS compatible

1 if (analysis("dc", "ic"))

2  out = ! V(in) > 0.0;

3 else

4  @(cross (V(in),0)) out = ! out

```

NEEDS compatibility does not allow the use of analysis dependent functions for the same reason it disallows event control statements: *model code should have no knowledge of which analysis is performed by the simulator*. Models should be able to work consistently in every analysis by providing the same DAE to the simulator. Converting and modifying the DAE is the simulators task and models should be transparent with regard to different types of

simulations and analyses. This transparency is one of the primary objectives of ModSpec. For more information about this subject, we refer the interested reader to [5, 6].

#### 6. DO use ddt, but only in allowed ways.

The ddt function is Verilog-A's way of denoting that an expression should be placed under the time derivation operator in the circuit DAEs. For instance, in Section 4, the capacitor charge in equation 2 should be denoted in Verilog-A as in Example 7.

```

EXAMPLE 7

NEEDS compatible

1 I (br_pn) <+ ddt (C*V(br_pn));

```

NEEDS compatibility has two rules regarding ddt usage:

- 1. The ddt function can only be used on the RHS of a contribution operator.

- 2. The entire charge (or flux) expression must go into the ddt function.

The purpose of both rules is to ensure that the system DAE can be properly constructed. Rule 1 enforces the principle that ddt is not used to compute the time derivative of a quantity in the model code but only indicates that the expression in the ddt function should be placed in the differential part of the DAE. Again, this procedure is handled by the simulator and not by the model.

```

NOT NEEDS compatible

1 i_disp = ddt (C* (V(br_pn));

2 I(br_pn) <+ i_disp;

NEEDS compatible

3 charge = C*V(br_pn);

4 I(br_pn) <+ ddt (charge);

```

The first case in Example 8 is not NEEDS compatible because it assigns the time derivative of a charge to a variable and then adds this variable to the branch current as a contribution. The second case (lines 3–4) shows how to do this in a NEEDS compatible manner. First the charge is computed and stored in a variable and then it is used in the ddt function in the contribution (line 4).

To understand the second rule above, consider a nonlinear capacitor with a quadratic voltage charge relationship  $(Q=C\,V^2)$ . This means that the model represents the following differential equation.

$$\frac{\mathrm{d}}{\mathrm{d}t}(CV^2) - I = 0 \tag{5}$$

```

NOT NEEDS compatible

1 I (br_pn) <+ C*pow(ddt(V(br_pn)), 2);

NEEDS compatible

2 I (br_pn) <+ ddt(C*(pow(V(br_pn), 2));

```

Line 1 in Example 9 shows a wrong attempt at implementing this model. In fact, this expression makes no mathematical sense either. The literal translation of this expression into a differential equation format would be

$$C\left[\frac{\mathrm{d}V}{\mathrm{d}t}\right]^2 - I = 0\tag{6}$$

which is not only different from equation (5) but also does not conform to the format of the circuit DAE formulation (see Section 4). The second line in Example 9 shows the correct Verilog-A implementation. In order to avoid this type of problem, NEEDS forbids the use of ddt *inside* other functions.

The best practice, when using a ddt statement, is to separate the ddt part of the contribution and collect all quantities that are part of the ddt statement together inside the argument of the ddt function. This is illustrated in Example 10 for an inductor model with a series resistor. The ddt contribution to V (br\_pn) is placed on a separate line and the constant L is written inside the ddt function.

```

NOT NEEDS compatible

1 V(br_pn) <+ R*I(br_pn) + L*ddt(I(br_pn));

NEEDS compatible

2 V(br_pn) <+ R*I(br_pn);

3 V(br_pn) <+ ddt(L*I(br_pn));

```

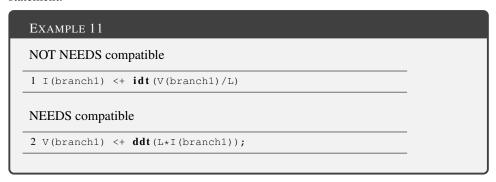

#### 7. DO NOT use idt.

Besides ddt, Verilog-A offers another function that can be used to specify the dynamical behavior of the model: idt. While ddt supplies the differential parts of the model equations, idt is meant to contribute to the *integral* parts. Therefore using ddt functions in a model would result in the following equation system<sup>11</sup>.

$$\frac{\mathrm{d}}{\mathrm{d}t}\vec{q} + \vec{f} + \int \vec{g}\,\mathrm{d}t = \vec{0} \tag{7}$$

However this formulation is not in the DAE format of equation (4). NEEDS compatibility forbids the use of idt. We explain the reasons below.

Every well-posed Verilog-A model can be defined without using the idt function. Consider a simple inductor model. The main model equation can be written using idt but it can also be written using idt as shown in Example 11. To achieve this, one only needs to exchange the potential and flow access functions (V () and I ()) on either side of the contribution statement.

The use of idt also poses a problem from an analysis standpoint. Consider DC analysis. In DC analysis, we solve for the steady state of a circuit. That means we assume that all time derivatives are zero and therefore drop the  $\vec{q}$  function in the DAE system. However, if the circuit equations were of the form in (7), what would that mean for the integral part of the equation? For instance, if the  $\vec{q}$  function has a constant nonzero term, the integral will be infinite and the entire system will be ill-posed. Therefore, in order to specify the dynamical model behavior, NEEDS compatibility requires models to exclusively use the ddt function.

#### 8. DO NOT use time-varying functions.

<sup>&</sup>lt;sup>11</sup>The distinction between  $\vec{f}_e$ ,  $\vec{f}_i$  and  $\vec{q}_e$ ,  $\vec{q}_i$  in equation (4) is dropped here for clarity.

```

1 analog begin

2 ...

3  V(branch1) <+ sin(2 * `M_PI * freq * $abstime);

4 ...

5 end</pre>

```

Example 12 shows a code snippet from a model that has a time-varying voltage assigned to one of its branches. This model uses the <code>\$abstime</code> simulator variable in order to reference the simulation time within the model. This makes the model unsuited for DC and AC analyses because "absolute time" does not make sense in these analysis types. In DC analysis, the circuit is assumed to have reached a steady state where the currents and voltages in the circuit do not change with time anymore. Therefore the concept of "absolute time" is not required in DC analysis. In AC analysis, the circuit is linearized around its DC solution and all subsequent computations are performed using *phasors* instead of time-varying quantities.

What a given simulator might do for these analyses is unclear — e.g., \$abstime variable may be assigned a value that is arbitrarily decided by the simulator, or the simulation may fail. The proper way to specify time-varying sources for each type of analysis is at the circuit netlist level. Verilog-A does not provide a mechanism for embedding time-varying sources into models. However, ModSpec provides a simple, general and elegant solution to this problem[5]. It is in this context that NEEDS compatibility requires that model developers do not use time-varying functions in their Verilog-A models. We do plan, however, to propose Verilog-A extensions for proper and general input support within models and to support them in our open-source toolchain (VAPP and MAPP).

#### 9. DO NOT use random number generators.

All device models must have a clearly defined deterministic part (in form of equation (4)) to be used in *all* analyses. Therefore NEEDS compatibility forbids the use of random number generator functions (such as \$dist\_uniform, \$dist\_normal etc.). Noise and parameter variability related analyses are exceptions to this rule, however in those cases only the form of randomness should be specified in the model (e.g. using \$white\_noise, \$flicker\_noise etc.) and all explicit random number generation should be left to the simulator. Putting random functions within the model description breaks the deterministic replicability of the model, and also its suitability for consistent use by every (deterministic) analysis in the simulator.

A good example of this situation can be found in the RRAM model presented in [14]. An excerpt of this model is given in Example 13.

#### EXAMPLE 13

Excerpt from the RRAM model presented in [14].

The gap variable in line 147 in Example 13 corresponds to a physical length in the device which grows over time. Instead of modeling the dynamics of this quantity with differential equations which are numerically integrated by the simulator, the developers of the model in [14] chose to perform the integration in the device model itself<sup>12</sup>. Moreover, this integration involves a random number that is also determined inside the device. The numerical integration of a random process is an intricate operation and the variance of the pseudorandom numbers used in this operation are directly connected to the integration time step. This is only one of the many reasons why the model code given in Example 13 will lead to problems during simulation and will possibly generate erroneous results. NEEDS compatibility requires that models do not contain any explicit random number generation code.

#### 10. DO take great care when using implicit equations.

Verilog-A allows implicit equations to be defined with the regular contribution format. While this is a feature that can be very useful if properly exercised, Verilog-A's syntax and constructs for implicit equations can be opaque and confusing to those unfamiliar with the underlying process of converting Verilog-A equations into DAEs. It is also possible to write Verilog-A code for implicit equations that makes no sense, as we have demonstrated in Section 3, which different simulators interpret differently and inconsistently. The first rule about implicit equations is: *try to avoid them if you can*. Therefore, it is strongly recommended that implicit equations in Verilog-A be avoided, unless the modeler has a good understanding of the mapping between Verilog-A model code and the underlying DAEs they correspond to. If implicit equations are desired, the following examples lay out how they can be implemented in a safe and unambiguous way.

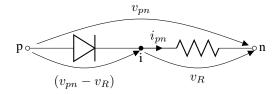

We again turn to the simple implicit diode example given in Section 3, Listing 6. This series circuit, consisting of an ideal diode and a resistor, is shown in Figure 5. In fact, this model can be described by explicit equations, as shown in Example 14.

<sup>&</sup>lt;sup>12</sup> For an exposition on how to do this properly, *i.e.*, using an extra internal unknown in the model, please see [12].

Fig. 5: Diode model with and ideal diode and a series resistor.

```

EXAMPLE 14

Figure 5 modeled with explicit equations.

1 module explicit_diode (p, n);

inout p, n;

electrical p, i, n;

branch (p, i) br_dio;

branch (i, n) br_res;

parameter real IS = 1e-12 from (0:inf);

parameter real R = 1 from (1e-3:inf);

analog begin

I(br_dio)) <+ IS*(limexp(V(br_dio)/$vt) - 1);</pre>

10

I(br_res) <+ V(br_res)/R;</pre>

11

end

12 endmodule

```

The Verilog-A model in example 14 consists of two contributions given in lines 9 and 10. Both of these are regular (explicit) contributions. The first one in line 9 quantifies the current flow through the ideal diode, between the nodes p and i in Figure 5. The second contribution in line 10 does the same for the current through the series resistor between the i and n nodes. However, because we have

$$v_{pi} = (v_{pn} - v_R) = (v_{pn} - R i_{pn}),$$

(8)

we can also construct this model as in Example 15.

#### EXAMPLE 15

Figure 5 modeled with an implicit equation.

```

1 module implicit_diode (p, n);

2    inout p, n;

3    electrical p, n;

4    branch (p, n) br_pn;

5    parameter real IS = 1e-12 from (0:inf);

6    parameter real R = 1 from (1e-3:inf);

7    analog begin

8    I(br_pn) <+ IS*(limexp((V(br_pn) - R*I(br_pn))/$vt) - 1);

9    end

10 endmodule</pre>

```

There are two things to note in the model given in Example 15. First, the internal node i has been eliminated. Second, the current I(p,n) appears on both sides of the contribution in line 8, which makes it implicit. The explicit model in Example 14 and the implicit model in Example 15 are mathematically equivalent. However, implicit equations have to be handled specially by the simulator. As noted above, it is easy to come up with constructs that make no sense. If implicit equations are used, it is important to abide by the following two NEEDS compatibility rules:

#### (a) DO NOT use a second contribution to an implicitly defined quantity.

```

EXAMPLE 16

NOT NEEDS compatible

1 I(br_pn) <+ IS*(limexp((V(br_pn) - R*I(br_pn))/$vt) - 1);

2 I(br_pn) <+ R2*I(br_pn);

```

The expression in Example 16 is undefined because it makes no sense from the perspective of DAE construction. Once I (br\_pn) is defined implicitly, it is not clear to what quantity the second contribution should be added. The first possible interpretation would be to add the second contribution to the first one and solve the equation

$$i_{pn} - I_s \left[ \lim \left( (v_{pn} - R i_{pn}) / v_t \right) - 1 \right] - R_2 i_{pn} = 0.$$

(9)

This is how Spectre handles it as we have seen in Section 3. The second possibility is to view I (br\_pn) as completely determined by the implicit contribution and ignore the explicit contribution in line 2 in Example 16. This would mean the simulator will solve the original implicit equation

$$i_{pn} - I_s \left[ \text{limexp} \left( (v_{pn} - R i_{pn}) / v_t \right) - 1 \right] = 0.$$

(10)

The third possible interpretation is to ignore the previous implicit contribution if there is an explicit contribution to the same branch. This is indeed how HSPICE interprets it. There is no formal reason to favor either one of these three possibilities since adding a second contribution to an implicitly defined quantity is inherently nonsensical. Therefore, NEEDS compatibility forbids a second contribution to a quantity once it is defined implicitly.

# (b) If you are using a "dummy probe", place it as the first expression on the right hand side of the implicit contribution.

```

NOT NEEDS compatible

1 V(branch1) <+ f(I(branch1) + I(branch2)) + V(branch1);

NEEDS compatible

2 V(branch1) <+ V(branch1) + f(I(branch1) + I(branch2));</pre>

```

Since Verilog-A contributions cannot have a zero on their LHS, V(branch1) in Example 17 acts as a "dummy probe" that facilitates the definition of the implicit equation for I(branch1) and I(branch2). Both expressions in Example 17 are equivalent to the following equation

$$f(i_{branch1} + i_{branch2}) = 0.$$

However, for clarity, NEEDS compatibility requires that the dummy probe appear as the first quantity on the RHS of an implicit contribution.

NEEDS recommends strongly that device modelers use implicit equations only if they know exactly what they are doing. Model developers are encouraged to confirm their equations are correct by examining the ModSpec code generated by VAPP on their model.

# 11. DO NOT allow any nodes in your model without having at least one branch with a well defined contribution attached to it.

Some models can contain nodes that naturally do not have any contributions to any of the branches involving that node. This is usually the case for controlled sources that use one of the nodes in the model as a probe to obtain information from the outside world, *i.e.*, the rest of the circuit.

If there are no currents flowing into (or out of) a node, this should explicitly be stated by writing down a zero contribution to one of its branches. Ideally, the second node of this branch will be the reference node of the model.

Consider the model in Example 18.

```

I module controlled_cap(n,qex,p);

2 inout p, qex, n;

3 electrical p, qex, n;

4 branch (p, n) br_pn;

5 branch (qex, n) br_qexn

6 analog begin

7 V(br_pn) <+ pow(V(br_qexn), 2);

8 end

9 endmodule

```

This is a voltage/charge controlled capacitor model that uses the qex node to receive voltage/charge information from some other node in the circuit. Although this model is complete in the above form, one should nevertheless explicitly state that there is no current flowing flowing through the branch br\_qexn. This is easily achieved by including a zero contribution to the model.

```

8    I(br_qexn) <+ 0;

```

Although the sensible choice for a compiler implementation is to handle these type of nodes as zero contribution nodes, it is always safer to state this fact explicitly. This way, the risk of running into undefined or compiler dependent behavior is minimized.

#### 12. DO NOT use bias-dependent switch branch and node collapse conditions.

Example 19 shows the use of a switch branch (taken from [1, Section 6.1]). Switch

branches use if/else statements in order to determine if a current contribution or a voltage contribution is to be made to a branch. However, the conditional expression of this if/else statement (V(ps,ns) > thresh) is bias-dependent, i.e., it changes during the operation of the circuit. The subsequent two contribution statements will result in a different number of unknowns in the circuit. This is because one of them probes a current variable and the other one a voltage variable. This means depending on the value of V(ps,ns), the number of variables in the device state vectors, i.e.,  $\vec{x}(t)$  and  $\vec{y}(t)$  in equation (4), have to be changed mid-simulation. This will break analyses such as shooting and harmonic balance that depend on combining system matrices under different bias conditions. Therefore, NEEDS compatibility forbids the use of switch branches with bias-dependent conditions.

After the construction of the DAE system from the input netlist, the numerical algorithms employed by the simulator operate on the equations in this system without any regard to the underlying circuit. For this reason, changing the number of current variables, for instance, at any time during a simulation will interfere with the operation of the numerical simulation algorithms. A NEEDS compatible device model will contribute the same number of equations with the same number of unknowns to the DAE no matter what its bias point is.

```

EXAMPLE 20

NOT NEEDS compatible

1 analog begin

2 ...

3 if (V(ctrl) > thresh)

4 V(out) <+ 0;

5 ...

6 end

```

A similar problem occurs if bias-dependent if/else conditions are used in combination with a *node collapse* statement. This is illustrated in Example 20 (taken from [7, Section 5.6.5]) Line 4 in Example 20 indicates that the out branch is to be collapsed if the condition in line 3 is satisfied. However, similar to Example 19, this condition is bias-dependent and will cause similar problems when constructing circuit DAEs. Therefore NEEDS compatibility does not allow node collapse statements with bias-dependent conditions.

The node collapse feature aims to achieve increased simulation performance by changing the number of nodes in a device in the case when a branch has no current or voltage contributions to it. By removing a node from the list of nodes in the device, one changes the size of the system DAEs. Since the system size has to stay constant during analyses, NEEDS compatibility only allows node collapse statements that have *bias-independent* conditions. Example 21 (excerpt from BSIM-4 [15]) shows a NEEDS compatible node collapse statement. In this case, the condition (RDSMOD == 0) depends solely on a parameter value, *i.e.*, is *bias-independent*.

```

EXAMPLE 21

NEEDS compatible

2 parameter real RDSMOD = 0 from [0:2];

3 analog begin

5

if (RDSMOD == 0)

6

begin

V(source, sourcep) <+ 0;

7

8

V(drainp, drain) <+ 0;

9

end

10

else

11

begin

12

I(drain, drainp) <+ type * gdtot * vded;</pre>

13

I(source, sourcep) <+ type * gstot * vses;</pre>

14

15

16 end

```

#### 13. DO use parameter ranges.

```

EXAMPLE 22

NEEDS compatible

1 parameter real R=1000 from (0:inf);

2 parameter real K=10 from (-inf:inf) exclude 0;

```

Parameter ranges are not a hard requirement for well-posed models but using them is good modeling practice. Using the from and exclude keywords as shown in Example 22 enables the simulator to check if the user assigned parameter values are within allowed limits. In Example 4, a resistance parameter, R, is restricted to strictly positive values and another parameter, K, is permitted to have negative values but is required to be nonzero. This way, the assignment of nonphysical values to parameters can be prevented. NEEDS compatibility requires that the range of every parameter is declared even if it is a trivial one such as (-inf:inf).

#### **6.2** Testing and Documentation Best Practices

An important requirement for NEEDS compatibility is that device models are tested in a number of ways, outlined below, the results of the testing documented, and the test scripts provided along

with the model so that any user can verify that the model passes the tests. NEEDS offers tools for easy and efficient testing of device models: NEEDS compatibility testing should be performed using the following NEEDS tools (additional testing with the commercial simulator Spectre, while not required, is recommended).

- VAlint: to assess the NEEDS compatibility of Verilog-A models.

- VAPP: to convert Verilog-A models into MAPP's ModSpec format.

- MAPP: to evaluate the performance of device models in various simulation algorithms.

The main NEEDS model development flow was outlined in Section 2, Figure 2. The crucial part of this flow is the first two steps where the model is developed in ModSpec format and iteratively tested using MAPP. The most important tests a model should be subjected to before it can be deemed *simulation ready* are listed below.

Make sure that your model produces sensible values for DC analysis at zero bias. DC

analysis is used in all simulations/analyses in order to find consistent initial conditions for

the circuit. Therefore, it is supremely important that your model produces sensible values

for DC bias conditions. Non-zero voltage/current output values at zero bias are typically

indicative of a modeling problem.

MAPP provides a script with the name model\_dc\_exerciser which takes a model as input and constructs a circuit with it by connecting all of its terminals to voltage/current sources. Using model\_dc\_exerciser, one can easily find out if a model has any problems at zero bias. For a hypothetical four terminal device, mos\_model\_under\_test, with terminal names d, g, s and b, we can simply run the script given in Listing 14.

Listing 14: Example usage of MAPP's model\_dc\_exerciser script.

```

MOD = mos_model_under_test(); % create an instance of the device

MEO = model_dc_exerciser(MOD); % initiate model exerciser

MEO.Id(0,0,0,0,MEO); % check drain current at zero bias

MEO.Ig(0,0,0,0,MEO); % check gate current at zero bias

MEO.Is(0,0,0,0,MEO); % check source current at zero bias

MEO.Ib(0,0,0,0,MEO); % check bulk current at zero bias

```

By running the code in Listing 14, we can find out if all of the terminal currents are in fact zero at zero bias. For instance, if the above code is executed, replacing the hypothetical model with the modified MVS model, version 1.0 from [16], we quickly discover that this model does not converge to a DC solution at zero bias and MAPP quits with the error.

```

NR: Jacobian is singular, aborting.

QSSsolve: failed after 2 iterations

```

This problem was discovered while testing the modified MVS model with MAPP and was fixed in a later version, v1.1.1, of the model<sup>13</sup>.

<sup>&</sup>lt;sup>13</sup>This updated version can be downloaded from https://nanohub.org/publications/95/3.

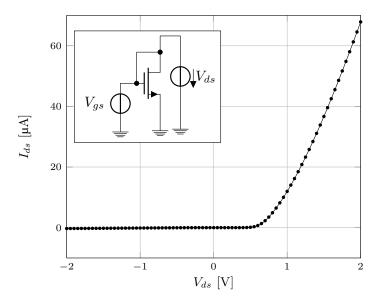

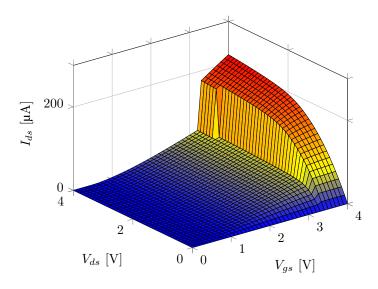

Fig. 6: DC sweep test using MAPP for the circuit shown in the inlay. The graph shows the drain-source current of the transistor plotted against the drain-source voltage.

#### 2. Conduct tests in which you connect all possible subsets of terminals together.

Test your model in all possible configurations, e.g., diode connect a transistor model (as shown in the inlay of Figure 6) and run simulations for that configuration. For a general device with n terminals, exercise every possible combination of connecting the terminals together and run DC sweeps over both positive and negative voltage values.

Listing 15: DC sweep in MAPP for the circuit in Figure 6.

```

1

% define nodes

cktnetlist.cktname = 'diode connected NMOS';

3

cktnetlist.nodenames = {'drain'};

4

cktnetlist.groundnodename = 'gnd';

5

% add voltage source to the circuit

6

cktnetlist = add_element(cktnetlist, vsrcModSpec(), 'Vdd',...

{'drain', 'gnd'}, {});

8

% create instance of transistor model and add it to the circuit

9

MOD = mos_model_under_test();

10

cktnetlist = add_element(cktnetlist, MOD, 'NMOS',...

{'drain', 'drain', 'gnd', 'gnd'}, {});

11

12

% create DAE from the circuit netlist

DAE = MNA_EqnEngine(cktnetlist);

13

% run dc sweep

14

dcSwObj = dcsweep(DAE, [], 'Vdd:::E', 0:0.01:2);

15

16

% plot results

[Vins, sols] = dcSwObj.getSolution(dcSwObj);

ipnIdx = DAE.unkidx('Vdd:::ipn', DAE);

```

```

19 plot(Vins, -sols(ipnIdx, :));

```

Listing 15 shows a MATLAB script that uses MAPP to test the circuit given in Figure 6 for a hypothetical transistor model,  $mos\_model\_under\_test$ . This piece of code first constructs the circuit (lines 2–11) and then runs a DC sweep on it where the voltage between the drain and source terminals of the transistor is increased from  $-2\,\mathrm{V}$  to  $2\,\mathrm{V}$ . The result of running this analysis with the BSIM-3 model is shown in Figure 6.