Ardent L. Bement Jr. Distinguished Lecture Fowler Hall, 10/29/2018

## **Moore's Law Extension and Beyond**

#### Peide (Peter) Ye

#### School of Electrical and Computer Engineering and

Birck Nanotechnology Center, Purdue University, West Lafayette, USA

#### Acknowledgement

**Prof. M.S. Lundstrom Purdue University**

Prof. M.A. Alam **Purdue University**

Prof. A. Shakouri **Purdue University**

**Prof. Dieter Weiss Prof. K. von Klitzing** Suzhou High School Regensburg University Max-Planck-Institute

Prof. J.C.M. Hwang Lehigh University

Prof. Daniel C. Tsui Dr. Kwok Ng **Princeton University Bell Labs/Lucent/Agere**

Mr. Yiran Wang

#### Acknowledgement

Purdue University: Dennis Lin (IMEC), J.J. Gu (Intel), Y.Q. Wu (IBM), Y. Xuan, J.Y. Zhang (IBM),

L. Dong (AMAT), Heng Wu (IBM), M. Si, M. Xu (AMAT), R.S. Wang (PKU),

X.F. Li (HUST), Han Liu (Intel), A.T. Neal (AFRL), Y. Deng (IBM), T. Shen (NIST),

L.M. Yang (Intel), Y. Du (GF), H. Zhou (UCB), Hagyoul Bae, Nathan Conrad,

Sami Al-ghamdi, G. Qiu, Adam Charnas, Wonil Chung, Jinhyun Noh, J.K. Qin,

Xiao Lyo, P.-Y. Liao, D. Zheng, C. Niu, Peter Bermel, Ali Shakouri, D. Zemlyanov,

Wenzhuo Wu, Haiyan Wang, Xianfan Xu, M.A. Alam, M.S. Lundstrom, and many others

SRC FCRP: D.A. Antoniadis (MIT), R.M. Wallace (UTD), A. Kummel (UCSD), S. Oktyabrsky (SUNY Albany), J. del Alamo (MIT)

SRC JUMP ASCENT Center: S. Datta (ND), D. Schlom (Cornell), S. Salahuddin (UCB), K.J. Cho (UTD)

IQE: W.K. Liu, J.M. Fastenau, D. Lubyshev ASM: G.D. Wilk SRC: K.K. Ng NTU: M. Hong and J. Kwo Yale University: T.P. Ma Harvard University: Y.Q. Liu (GF), X.W. Wang (PKU), R.G. Gordon Lehigh University: J.C.M. Hwang Fudan: M.F. Li and D.M. Huang U. Padova: N. Wrachien, E. Zanoni, G. Meneghesso SEMATECH: K. Majumdar, C. Hobbs TSMC: W. Tsai, Y.M. Li, Lance Li

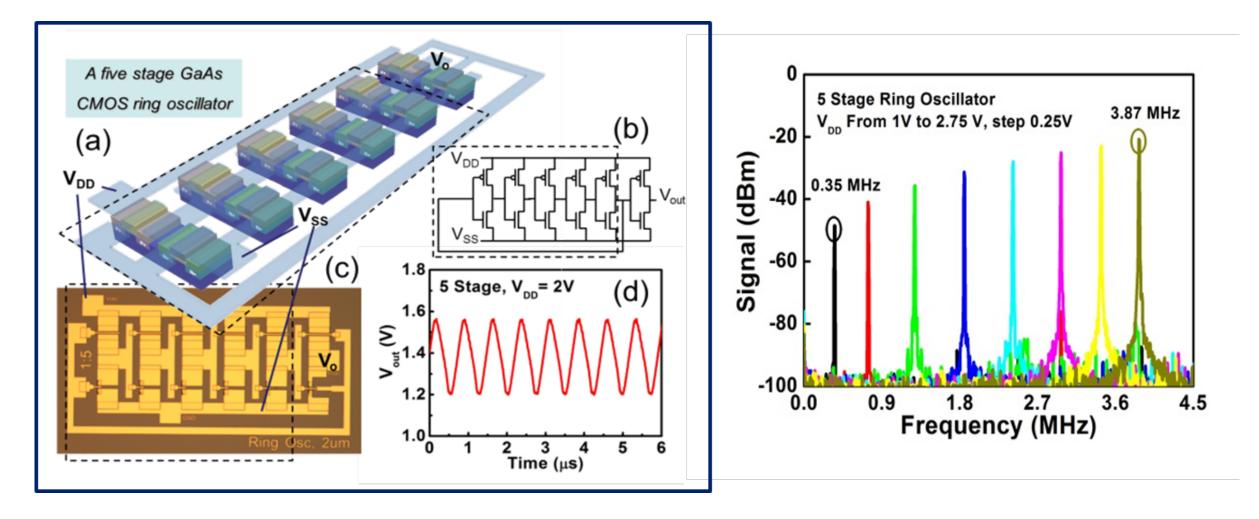

# Outline

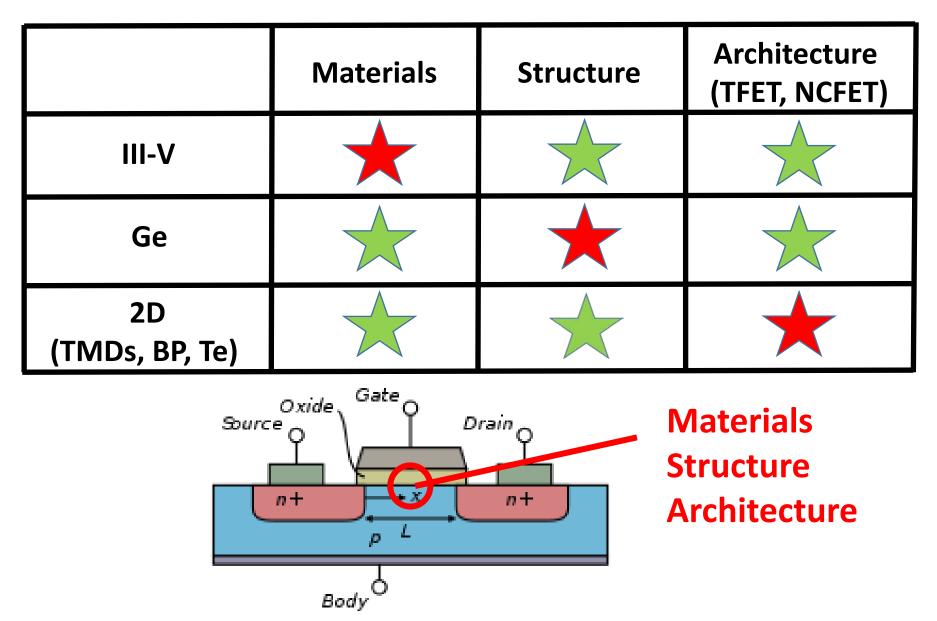

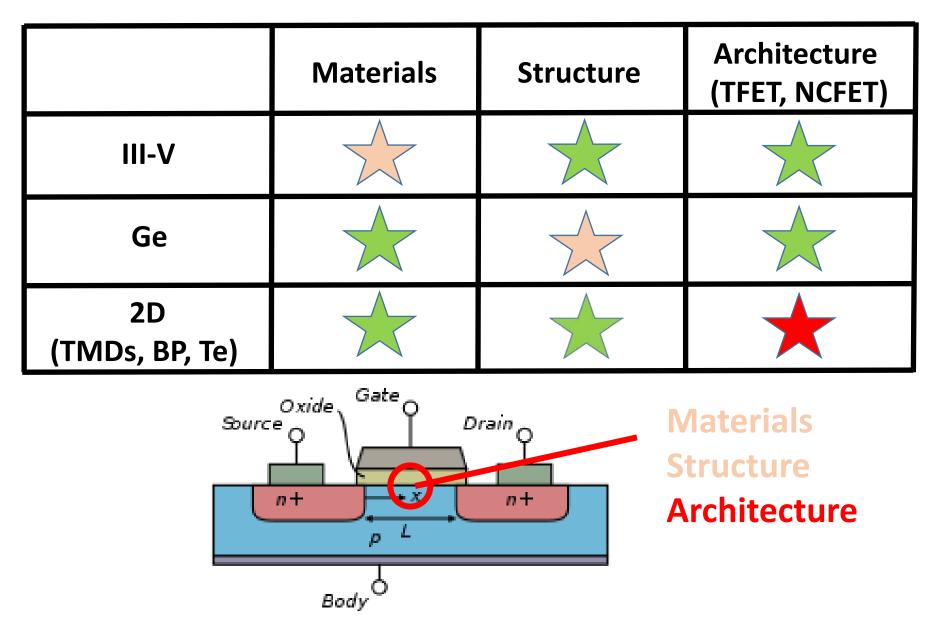

- Introduction of Moore's Law in Microelectronics

- Materials Innovation

- III-V Metal-oxide-semiconductor Field-effect transistors (MOSFETS)

#### Structure Engineering

Ge 3D Gate-all-around Field-effect Transistors (GAAFETs)

#### Device Architecture Exploration

2D Negative Capacitance Field-effect Transistors (NCFETs)

Conclusion and Outlook

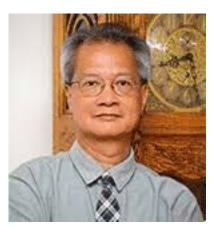

#### **History of Computation**

SOURCE: RAY KURZWEIL, "THE SINGULARITY IS NEAR: WHEN HUMANS TRANSCEND BIOLOGY", P.67, THE VIKING PRESS, 2006. DATAPOINTS BETWEEN 2000 AND 2012 REPRESENT BCA ESTIMATES.

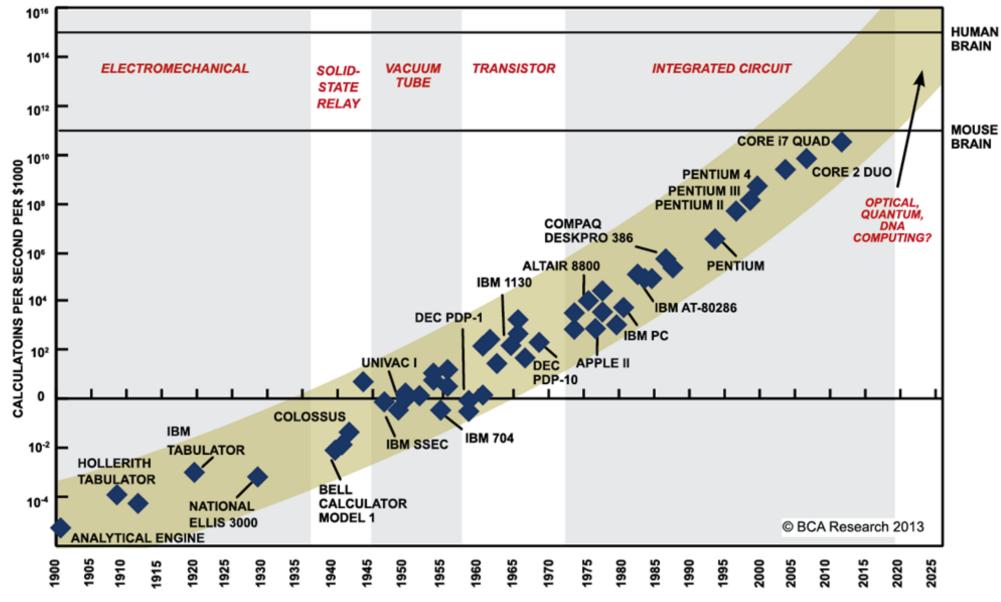

#### **Moore's Law in Microelectronics**

Data source: Wikipedia (https://en.wikipedia.org/wiki/Transistor\_count)

© 2000 Nigel Tout

The data visualization is available at OurWorldinData.org. There you find more visualizations and research on this topic.

### Power, Power, Power!

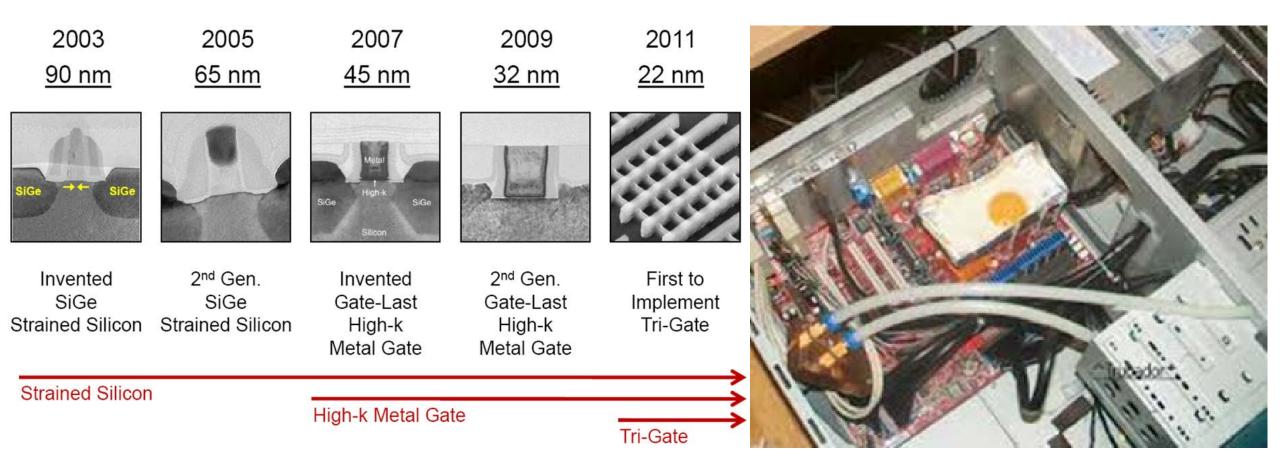

## **Research on Moore's Law Extension**

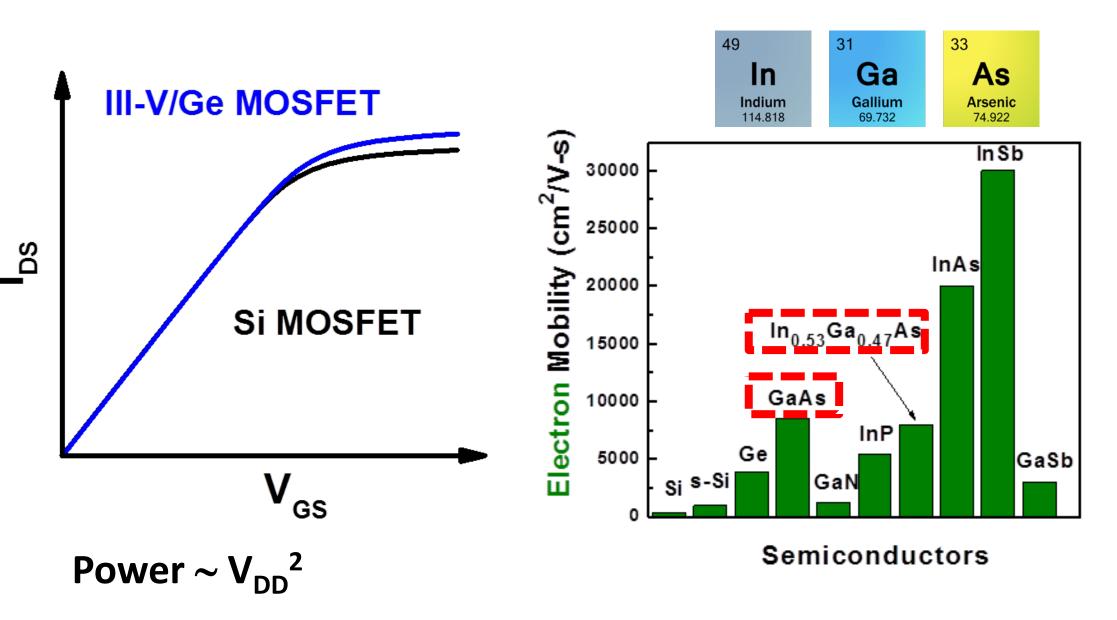

## Why III-V MOSFET for Logic Applications

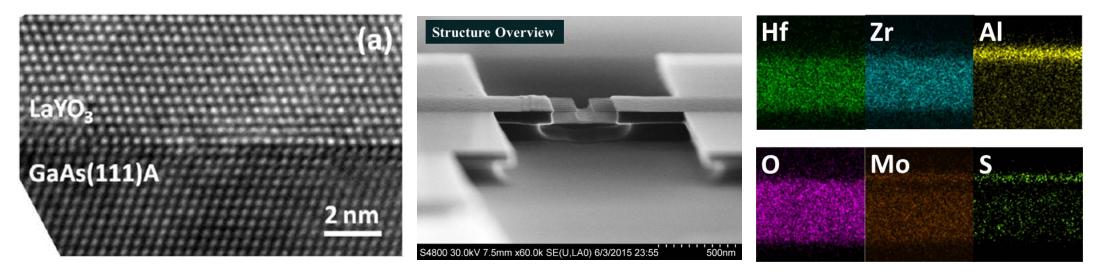

# **Oxide layer formation on GaAs**

#### **Native Oxides**

- (1) Thermal oxidation of GaAs

- (2) Wet oxidation of GaAs

- (3) Plasma oxidation of GaAs

- (4) Laser-assisted oxidation of GaAs

- (5) Vacuum ultraviolet photochemical oxidation of GaAs

#### **Deposited Oxides**

- (6) CVD deposited oxide films on GaAs

- (7) Si/Ge interficial layer + oxide films

- (8) MBE deposited oxide films on GaAs  $(Ga_2O_3-Gd_2O_3)$

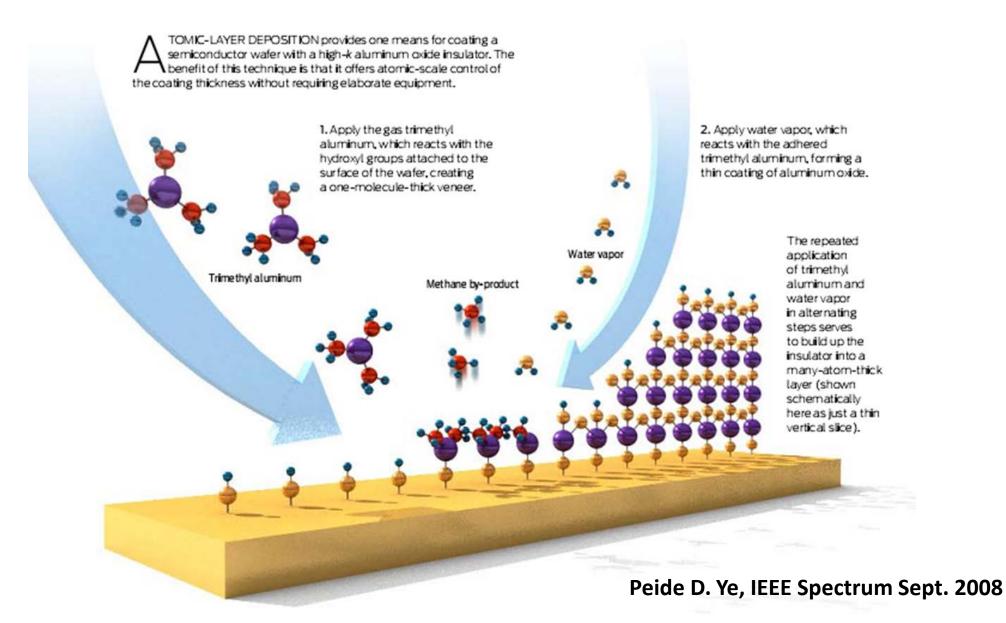

- (9) <u>Atomic Layer Deposition (ALD) grown</u> oxide films on III-V semiconductors

**A Dream for more than Four Decades**

1979 Takashi Mimura at Fujitsu Laboratories in Japan invents HEMT

1979 W.E. Spicer experimentally confirms "oxide"/GaAs(110) Fermi-level pinning; All agencies in DoD/USA stop funding III-V MOSFET research. (T.P. Ma SISC 2009 talk)

> III-V MOSFET research is still going at small scale in the end of 80s and 90s

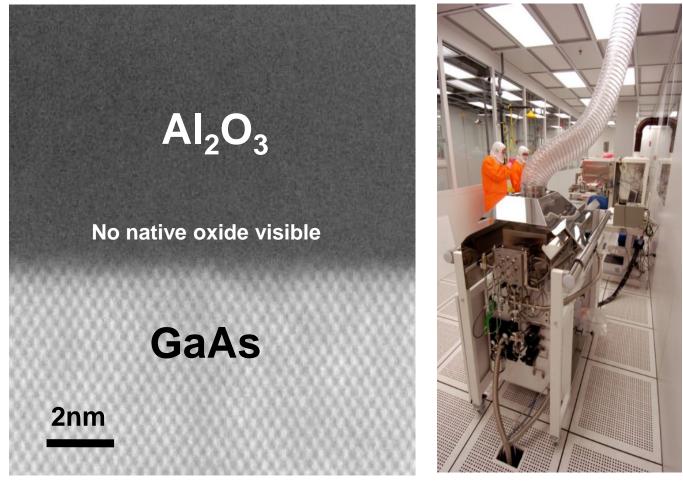

## **Ex-situ** ALD high-k on III-V substrates

2002 Ye, Wilk and others started to study ALD Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> process on III-V

ALD self-cleaning effect 2 ASM ALD Systems at Purdue

Many works at Intel, IBM, SEMATECH, IMEC, AIST, Purdue, U. Tokyo, Stanford, MIT, UCB, UCSB, UCSD, NUS, UT Austin, UT Dallas, NTHU, many other universities

# ALD $AI_2O_3$ Process with TMA and $H_2O_3$

12

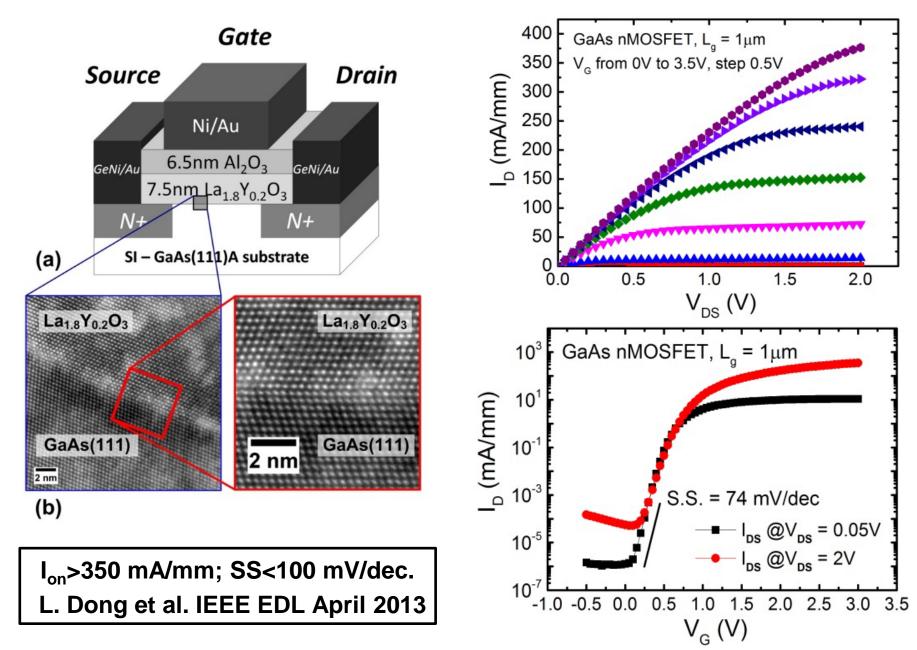

#### Highest $I_D$ in GaAs MOSFET enabled by ALD

13

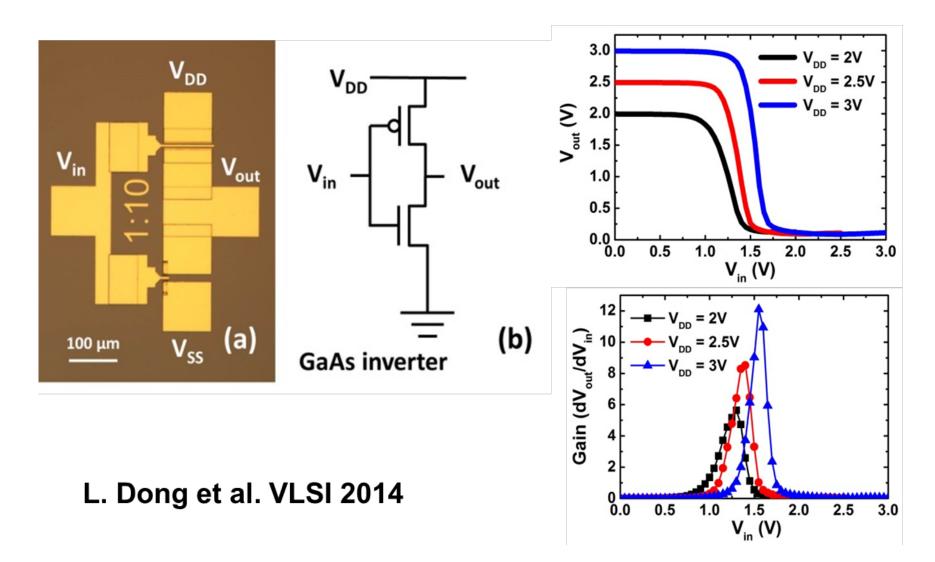

## **First GaAs CMOS Inverter**

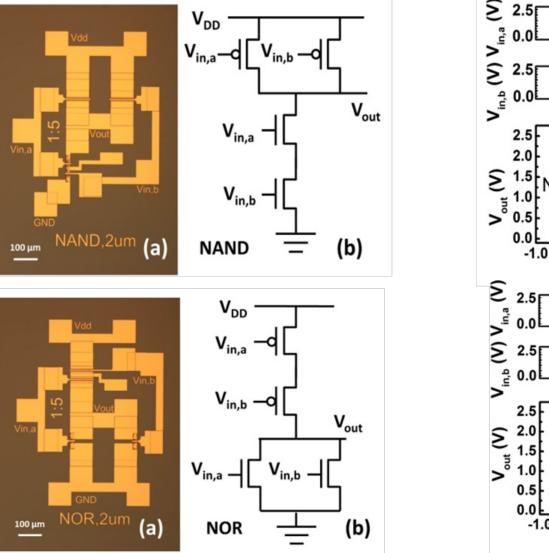

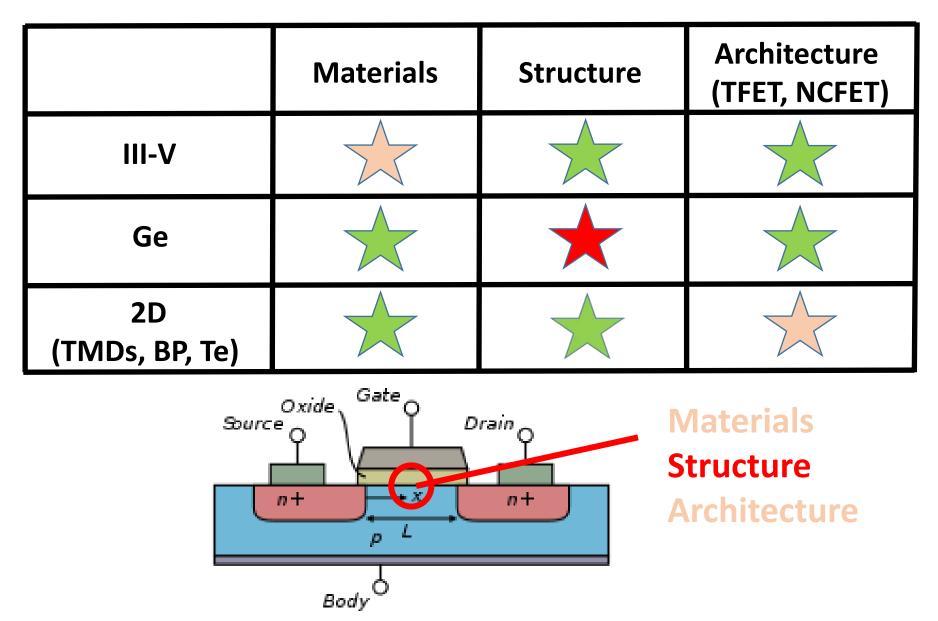

#### First GaAs CMOS based circuitry

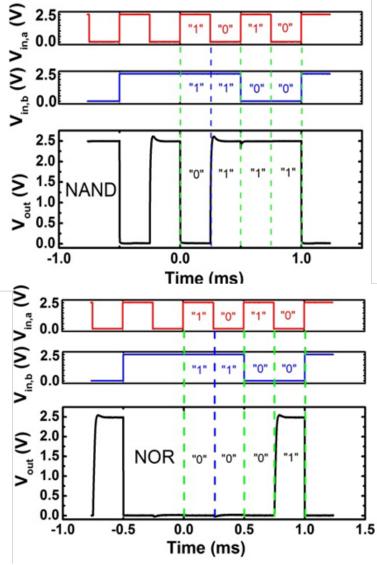

### First GaAs CMOS 5-Stage Ring-Oscillator

L. Dong et al. VLSI 2014 16

## **Research on Moore's Law Extension**

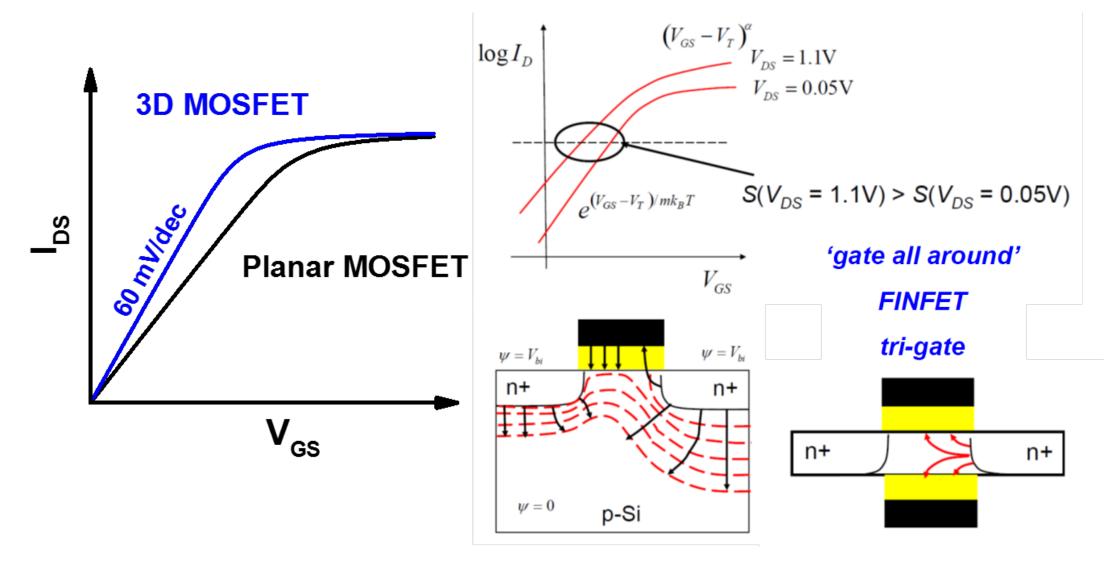

#### **3D Transistors improve electrostatic control of the channel**

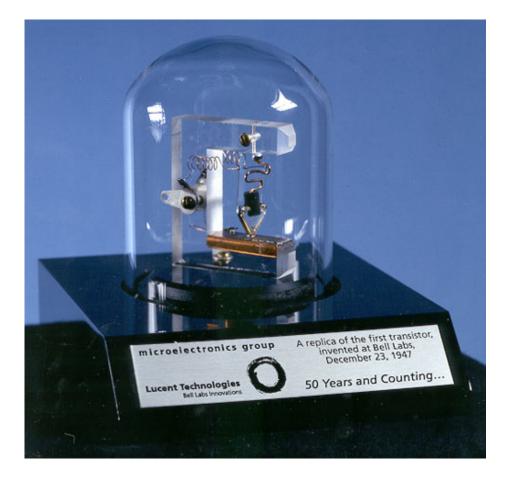

# The First Transistor is on Ge (made at Purdue)

The first point contact transistor invented by Bardeen and Brattain at Bell Labs in 1947

Karl Lark-Horovitz (1892-1958) was hired by Purdue since 1928

## **Advanced Gate Structures (Gate-all-around)**

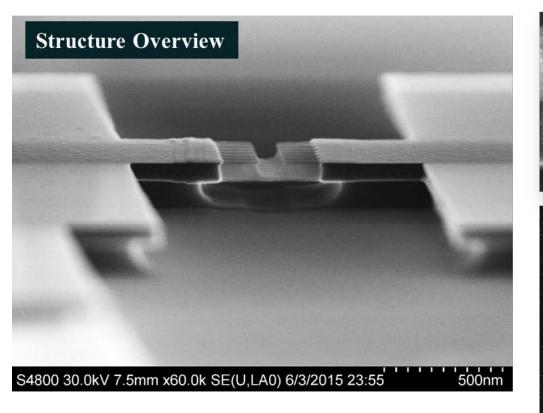

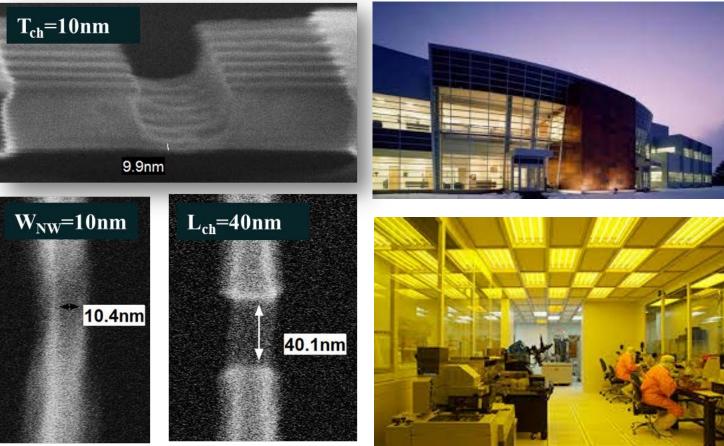

#### • Ge Nanowire CMOS SEMs

□ Ge Nanowire CMOS Devices demonstrated □  $T_{ch}$ = 10 nm, smallest  $W_{NW}$  = 10 nm, and  $L_{ch}$  = 40 nm

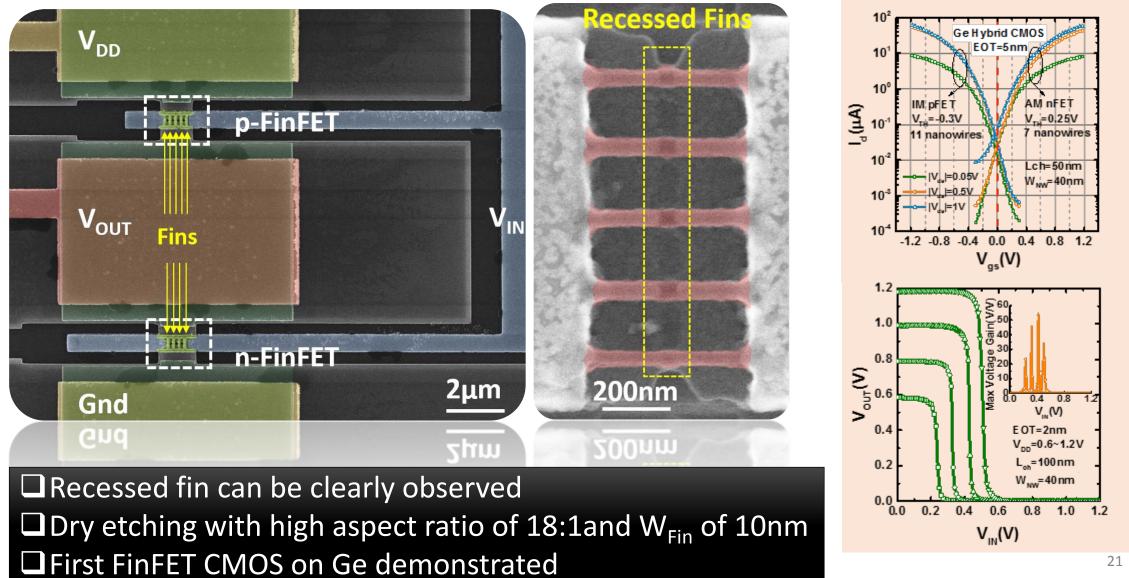

## First Ge CMOS Circuits with 3D Structures

#### **FinFET CMOS Under SEM**

#### **Advanced Gate Structures**

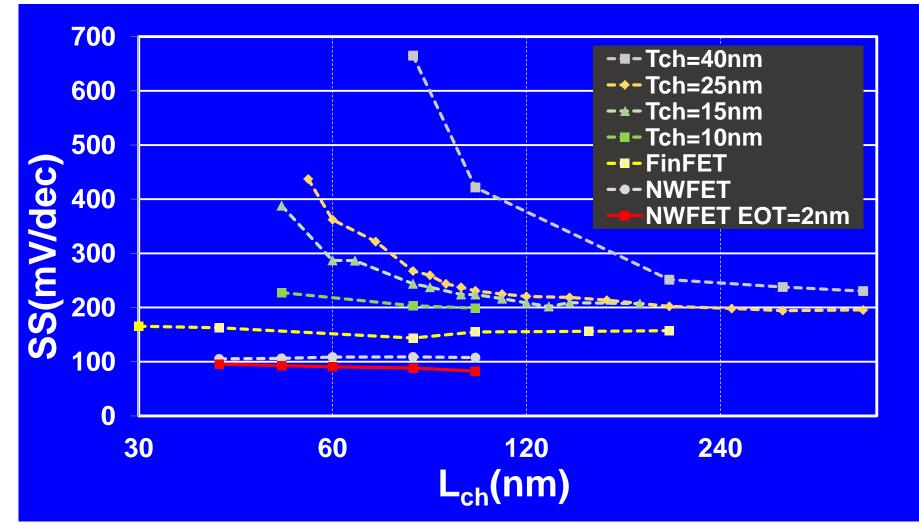

#### Short Channel Effect Immunity

□ SS is reduced down to around 80 mV/dec in nanowire devices with small EOT

## **Research on Moore's Law Extension**

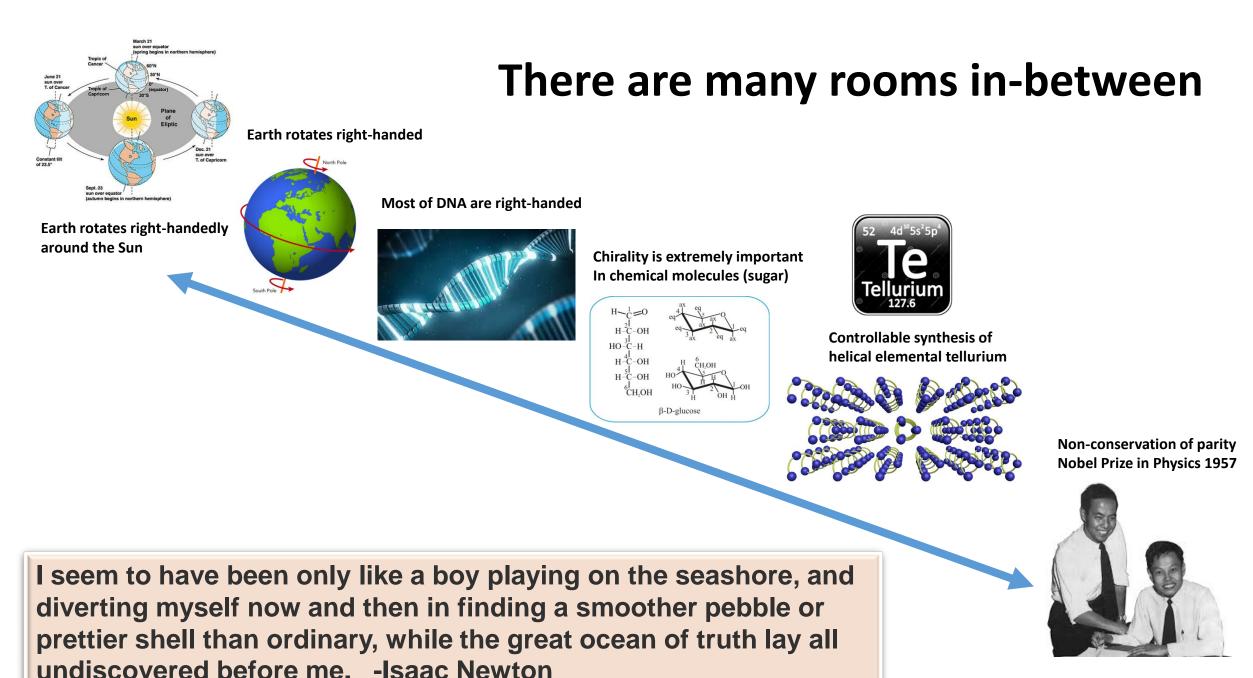

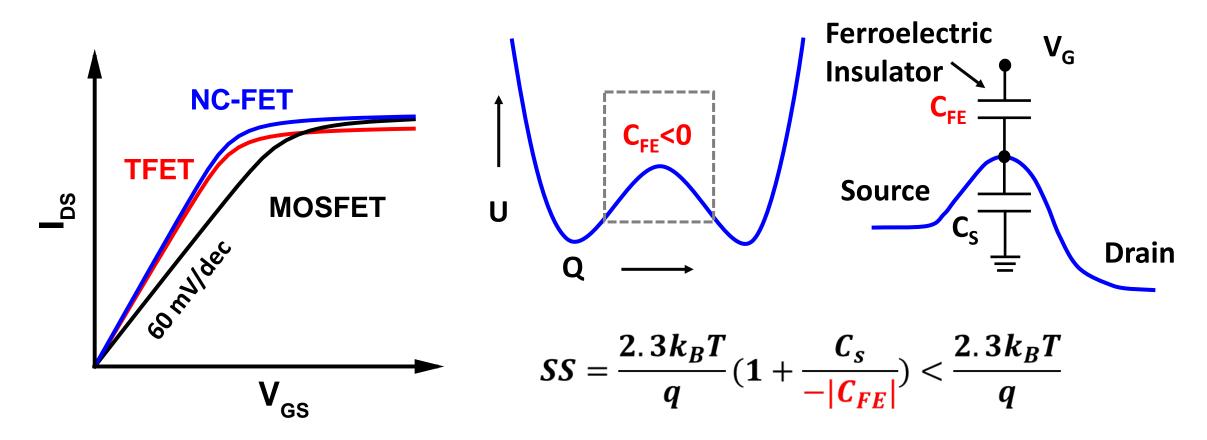

### **Steep-slope Switches for Low-power Applications**

□ NC-FETs can achieve steep-slope switching without on-state degradation.

S. Salahuddin and S. Datta, Nano Lett., 2008 <sup>24</sup>

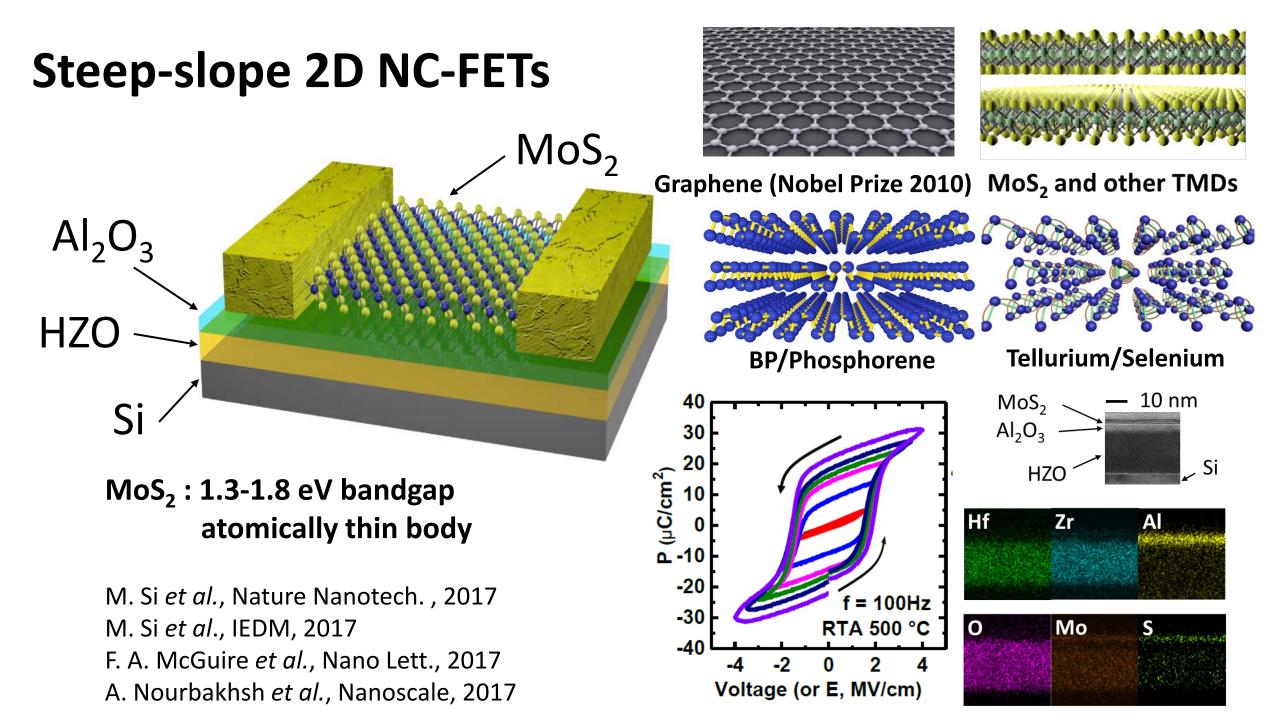

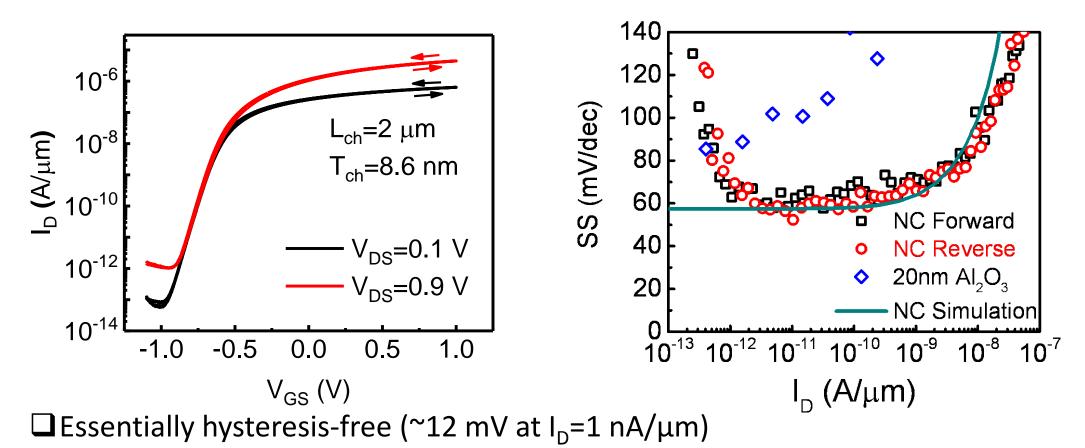

# Steep-slope MoS<sub>2</sub> NC-FETs with HZO as Gate Dielectric: DC Electrical Characterization

□ Sub-60 mV/dec subthreshold slope at room temperature

(1) Bi-directionally SS < 60 mV/dec; (2) Hysteresis-free;

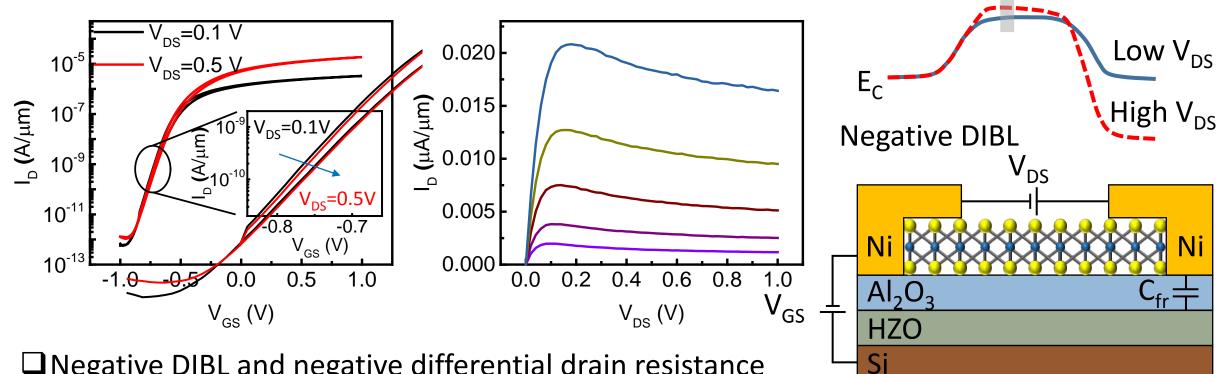

#### **Negative DIBL and Negative Differential Resistance**

Negative DIBL and negative differential drain resistance observed as the result of drain negative capacitance coupling.

H. Ota et al., IEDM 2016

(3) Negative DIBL; (4) Negative Differential Drain Resistance at Low Current;

# Conclusions

- Purdue University is always a front-runner and power-house for semiconductor materials and device research.

- Moore's Law in microelectronics is slowing down, but will be continuing. Innovative research for new types of switches are strongly demanded. Purdue has three new centers on that front in 2018.

- Academia can contribute significantly on this research front. Hopefully some of our research can have significant impacts on science, industry and even human society.