## ME290R: Topics in Manufacturing Fall 2017

### Nanoscale manipulation of materials

Lecture 2.2: Lithography Performance Criteria - Point Defects (Yield Modeling)

August 28, 2017

Hayden Taylor hkt@berkeley.edu

# What factors need to be borne in mind when evaluating a lithography process?

### Technical

- Dimensional accuracy and variability

- Pattern edge roughness

- Overlay accuracy

- Point defects

#### Economic

- Throughput (vs. yield)

- Materials, tooling, equipment, and energy costs

### Environmental

- Materials usage and disposal (toxicity)

- Energy used in process

- Embodied energy

| Yield unsdeling                                                       | nofer                                                                    |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------|

| Characterize yield at several stages (scales                          |                                                                          |

| - Wafer yield - how many make it to probing?                          |                                                                          |

| - Probe-testig Simple electrical testing                              | chip                                                                     |

| - final testing - built in test structures.                           | different circuit blocks may have different defect responses.  Core cloc |

| - Dre-by-dre (dip-dip)                                                |                                                                          |

| - functioned y'eld / "hard" -> bir<br>-> parametric yield ( "soft" -> | max clock speed? "binning"                                               |

|                                                                       | Core-scale characterisation?                                             |

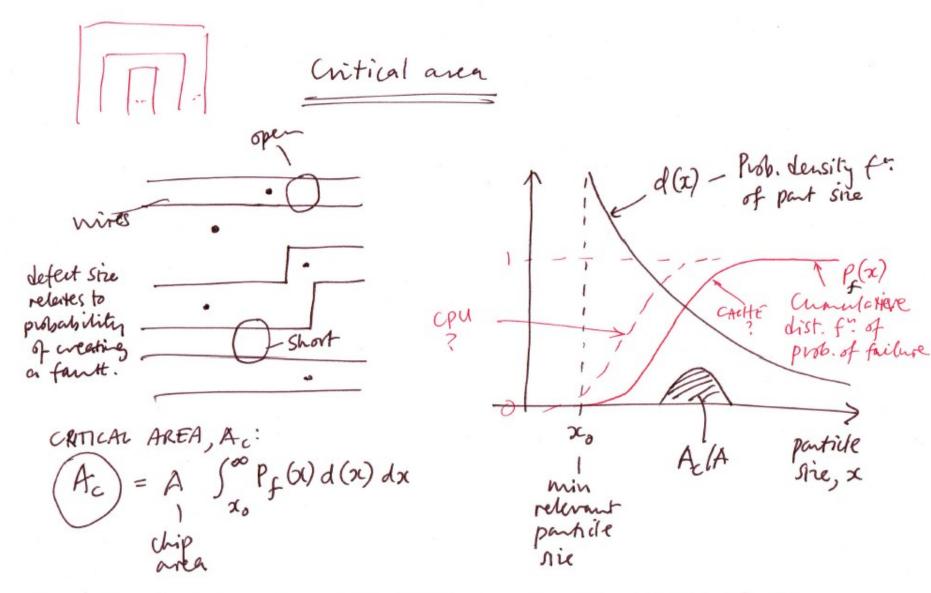

Suppose Do is average of defects per unit area leading to a fault Expected of defects on wafer  $M = A_C D_O C$ \* thips on wafer

Yield modeling continued ...

- Possible permutations of the latations of the M defects

- If one dip is defet-free, # permetations is now (C-1) M

: probability that a given chip is defeat- free: (C-1)m = (1-1)M

Yield = lim (1-1) CACPO = exp(-AcDo)

(frauhas of chips hat make)

property Property of process

Probability of N clips having no defects:  $\exp(-A_c D_o)^N = \exp(-N A_c D_o)$

# How can we characterize manufactured patterns?

- Dimensionally

- Scanning electron microscopy

- Atomic force microscopy

- Optically: microscopy, scatterometry, interferometry

- Functionally

- Electrical measurements e.g. serpentine test structures

- Optically, in the case of optical interconnect

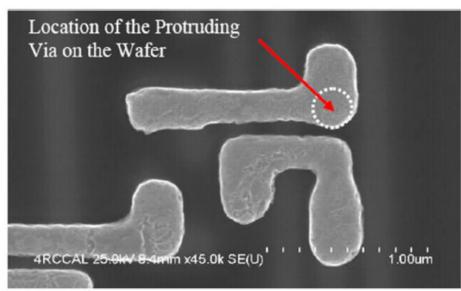

### Scanning electron microscopy: CDSEM

- Widespread use in semiconductor metrology

- Top-down imaging can give CD and LER information without destroying the wafer

- For cross-sectional (sidewall angle) information, cross-sectioning (typically with focused ion beam (FIB) milling) is needed

http://www.eejournal.com/archives/articles/ 20101026-synopsys/?printView=true

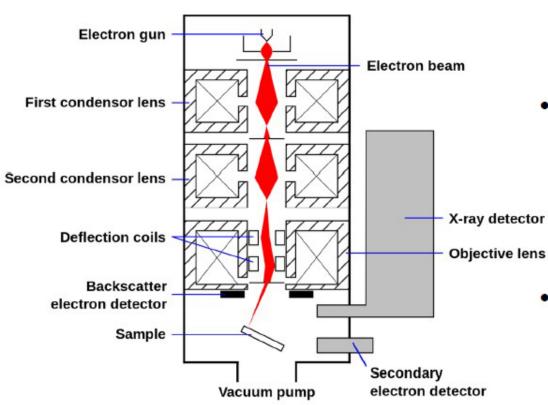

### CD SEM – working principle

- Resolution < 1 nm</li>

- Can determine topography and chemical composition

- Raster scanning of sample

- Both backscattered and secondary electrons can be sensed and used to create an image

- Secondary electrons are ejected from the sample atoms as a result of inelastic scattering interactions with beam electrons

- Backscattered electrons are reflected beam electrons – used to detect chemical composition

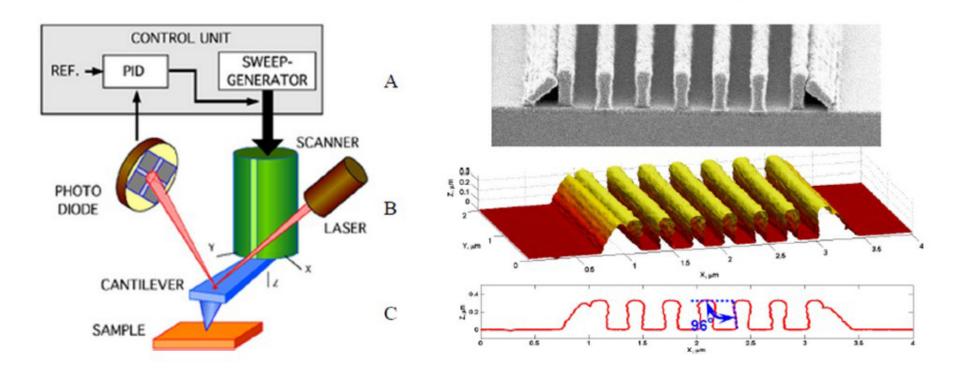

## Atomic force microscopy

- Potential to give some sidewall information without sectioning the wafer

- However, the measurement obtained is the convolution of tip shape with the true topography.

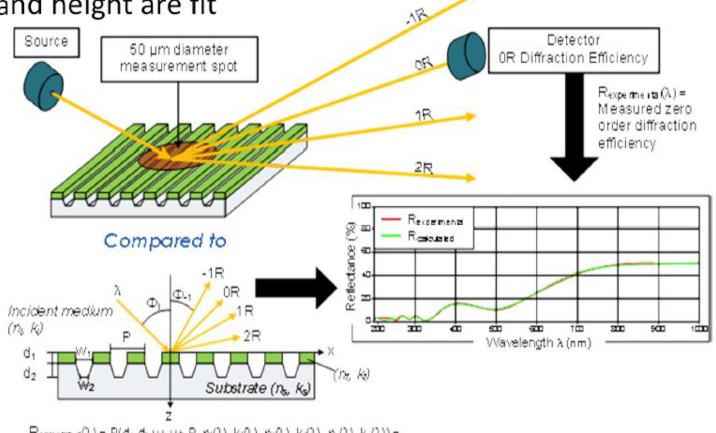

# Scatterometry – gathers average pattern geometry information from arrays of features

Scattered intensities at several diffraction orders or wavelengths are compared to a model – geometric parameters such as CD, sidewall angle, and height are fit

Resonant  $(\lambda) = R(d_1 d_2 w_1 w_2 P, n_i(\lambda), k_i(\lambda), n_i(\lambda), k_i(\lambda), n_i(\lambda), k_i(\lambda)) = Calculated zero order (OR) diffraction efficiency$

http://www.halbleiter.org/en/oxidation/metrology/

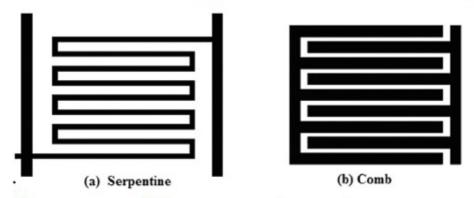

## Electrical/functional test structures

- Basic electrical test structures

- Serpentine detect open circuits

- Comb detect short circuits

- Must cover a large enough area to offer a reasonable probability of detecting an error without encountering an error on every chip

BIST – Built-In Self-Test circuits